# Exhibit A

US007289386B2

### (12) United States Patent

### Bhakta et al.

### (54) MEMORY MODULE DECODER

- (75) Inventors: Jayesh R. Bhakta, Cerritos, CA (US); Jeffrey C. Solomon, Irvine, CA (US)

- (73) Assignee: Netlist, Inc., Irvine, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 21 days.

- (21) Appl. No.: 11/173,175

- (22) Filed: Jul. 1, 2005

#### (65) **Prior Publication Data**

US 2006/0062047 A1 Mar. 23, 2006

### **Related U.S. Application Data**

- (63) Continuation-in-part of application No. 11/075,395, filed on Mar. 7, 2005.

- (60) Provisional application No. 60/588,244, filed on Jul. 15, 2004, provisional application No. 60/575,595, filed on May 28, 2004, provisional application No. 60/550,668, filed on Mar. 5, 2004.

- (51) Int. Cl.

### *G11C 8/00* (2006.01)

- (52) U.S. Cl. ..... 365/230.06; 365/51; 365/230.08

See application file for complete search history.

### (56) **References Cited**

### U.S. PATENT DOCUMENTS

| 4,392,212 A | * | 7/1983 | Miyasaka et al 365/2 | 230.06 |

|-------------|---|--------|----------------------|--------|

| 5,247,643 A |   | 9/1993 | Shottan              |        |

| 5,426,753 A | * | 6/1995 | Moon                 | 711/5  |

### (10) Patent No.: US 7,289,386 B2

### (45) **Date of Patent:** Oct. 30, 2007

| 5,703,826 A | 12/1997   | Hush et al.        |

|-------------|-----------|--------------------|

| 5,805,520 A | 9/1998    | Anglada et al.     |

| 5,959,930 A | * 9/1999  | Sakurai 365/230.03 |

| 6,154,418 A | 11/2000   | Li                 |

| 6,453,381 B | 1 9/2002  | Yuan et al.        |

| 6,518,794 B | 2 2/2003  | Coteus et al.      |

| 6,681,301 B | 1 1/2004  | Mehta et al.       |

| 6,785,189 B | 2 8/2004  | Jacobs et al.      |

| 6,807,125 B | 2 10/2004 | Coteus et al.      |

| 6,813,196 B | 2 11/2004 | Park et al.        |

### (Continued)

#### OTHER PUBLICATIONS

Barr, Michael. "Programmable Logic: What's it to Ya?," Embedded Systems Programming, Jun. 1999, pp. 75-84. Retrieved by Examiner from http://www.netrino.com/Articles/ProgrammableLogic/index.php.\*

(Continued)

Primary Examiner—Son Dinh

Assistant Examiner-Alexander Sofocleous

(74) Attorney, Agent, or Firm-Knobbe Martens Olson & Bear LLP

### (57) **ABSTRACT**

A memory module connectable to a computer system includes a printed circuit board, a plurality of memory devices coupled to the printed circuit board, and a logic element coupled to the printed circuit board. The plurality of memory devices has a first number of memory devices. The logic element receives a set of input control signals from the computer system. The set of input control signals corresponds to a second number of memory devices smaller than the first number of memory devices. The logic element generates a set of output control signals in response to the set of input control signals. The set of output control signals corresponds to the first number of memory devices.

### 13 Claims, 18 Drawing Sheets

### U.S. PATENT DOCUMENTS

| 6044604      | DO     | 0/0005  | D                  |

|--------------|--------|---------|--------------------|

| 6,944,694    | В2     | 9/2005  | Pax                |

| 6,981,089    | B2 *   | 12/2005 | Dodd et al 710/308 |

| 6,982,893    | B2 *   | 1/2006  | Jakobs 365/63      |

| 6,996,686    | B2     | 2/2006  | Doblar et al.      |

| 7,046,538    | B2 *   | 5/2006  | Kinsley et al      |

| 7,120,727    | B2 *   | 10/2006 | Lee et al 711/5    |

| 7,200,021    | B2 *   | 4/2007  | Raghuram 365/51    |

| 2001/0052057 | A1     | 12/2001 | Lai et al.         |

| 2002/0088633 | A1     | 7/2002  | Kong et al.        |

| 2003/0063514 | A1     | 4/2003  | Faue               |

| 2003/0191995 | A1     | 10/2003 | Abrosimov et al.   |

| 2003/0210575 | A1     | 11/2003 | Seo et al.         |

| 2004/0037158 | A1     | 2/2004  | Coteus et al.      |

| 2005/0036378 | A1     | 2/2005  | Kawaguchi et al.   |

| 2005/0281096 | A1     | 12/2005 | Bhakta et al.      |

| 2006/0126369 | A1*    | 6/2006  | Raghuram 365/51    |

| 2006/0129755 | A1 $*$ | 6/2006  | Raghuram 711/105   |

### OTHER PUBLICATIONS

Cuppu, Vinodh, et al., "A Performance Comparison of Contemporary DRAM Architectures," *IEEE Proceedings of the 26<sup>th</sup> International Symposium on Computer Architecture*, May 2-4, 1999, Atlanta, Georgia, pp. 1-12. JEDEC Standard No. 21-C, 4.20-2—168 Pin, PC133 SDRAM Registered Design Specification, Revision 1.4, Release 11a, Feb. 2002.

JEDEC Standard No. 21-C, 4.20-3—144 Pin, PC133 SDRAM Unbuffered SO-DIMM, Reference Design Specification, Revision 1.02, Release 11.

JEDEC Standard No. 21-C, DDR SDRAM PC2100 and PC1600 DDR SDRAM Registered DIMM Design Specification, Revision 1.3, Release 11b, Jan. 2002.

JEDEC Standard No. 21-C, 4.20.5—184 Pin, PC1600/2100 DDR SDRAM Unbuffered DIMM Design Specification, Revision 1.1, Release 11b.

JEDEC Standard No. 21-C, 4.20.6—200 Pin, PC2700/PC2100/ PC1600 DDR SDRAM Unbuffered SO-DIMM Reference Design Specification, Revision 1.1, Release 11b, Apr. 26, 2002.

JEDEC standard JESD79D, "Double Data Rate (DDR) SDRAM Specification," published Feb. 2004.

Intel Corporation, PC SDRAM Registered DIMM Design Support Document, Revision 1.2, Oct. 1998.

Intel Corporation, 66/100 MHz PC SDRAM 64-Bit Non-ECC/ Parity 144 Pin Unbuffered SO-DIMM Specification, Revision 1.0, Feb. 1999.

U.S. Appl. No. 11/173,175, filed Jul. 1, 2005, Bhakta et al.

\* cited by examiner

### FIG. 1C

FIG. 2A

FIG. 2B

FIG. 3A

FIG. 3B

FIG. 4A

FIG. 6B

FIG. 6D

FIG. 6E

Time

FIG. 12B

ODT

505

,510 514 500 518 -75Ω DQ 576 552 \_ 556 512\_ VTT *75*Ω 572 DQS -516 520 524 *522* -526 75Ω 52<u>8</u> 574 `~ 558 554 DQ VTT *75*Ω 578 538 *75*Ω 530

536

534

*560* VTT

30

### MEMORY MODULE DECODER

### CROSS-REFERENCE TO RELATED APPLICATIONS

The present application is a continuation-in-part of U.S. patent application Ser. No. 11/075,395, filed Mar. 7, 2005, which claims the benefit of U.S. Provisional Application No. 60/550,668, filed Mar. 5, 2004 and U.S. Provisional Application No. 60/575,595, filed May 28, 2004. The present 10 application also claims the benefit of U.S. Provisional Application No. 60/588,244, filed Jul. 15, 2004, which is incorporated in its entirety by reference herein.

### BACKGROUND OF THE INVENTION

1. Field of the Invention

The present invention relates generally to memory modules of a computer system, and more specifically to devices and methods for improving the performance, the memory <sub>20</sub> capacity, or both, of memory modules.

2. Description of the Related Art

Certain types of memory modules comprise a plurality of dynamic random-access memory (DRAM) devices mounted on a printed circuit board (PCB). These memory modules <sub>25</sub> are typically mounted in a memory slot or socket of a computer system (e.g., a server system or a personal computer) and are accessed by the processor of the computer system. Memory modules typically have a memory configuration with a unique combination of rows, columns, and <sub>30</sub> banks which result in a total memory capacity for the memory module.

For example, a 512-Megabyte memory module (termed a "512-MB" memory module, which actually has 2<sup>29</sup> or 536, 870,912 bytes of capacity) will typically utilize eight 512- 35 Megabit DRAM devices (each identified as a "512-Mb" DRAM device, each actually having 2<sup>29</sup> or 536,870,912 bits of capacity). The memory cells (or memory locations) of each 512-Mb DRAM device can be arranged in four banks, with each bank having an array of  $2^{24}$  (or 16,777,216) 40 memory locations arranged as 213 rows and 211 columns, and with each memory location having a width of 8 bits. Such DRAM devices with 64M 8-bit-wide memory locations (actually with four banks of 2<sup>27</sup> or 134,217,728 one-bit memory cells arranged to provide a total of 2<sup>26</sup> or 67,108, 45 864 memory locations with 8 bits each) are identified as having a "64 Mb×8" or "64M×8-bit" configuration, or as having a depth of 64M and a bit width of 8. Furthermore, certain commercially-available 512-MB memory modules are termed to have a "64M×8-byte" configuration or a 50 "64M×64-bit" configuration with a depth of 64M and a width of 8 bytes or 64 bits.

Similarly, a 1-Gigabyte memory module (termed a "1-GB" memory module, which actually has  $2^{30}$  or 1,073, 741,824 bytes of capacity) can utilize eight 1-Gigabit 55 DRAM devices (each identified as a "1-Gb" DRAM device, each actually having  $2^{30}$  or 1,073,741,824 bits of capacity). The memory locations of each 1-Gb DRAM device can be arranged in four banks, with each bank having an array of memory locations with  $2^{14}$  rows and  $2^{11}$  columns, and with 60 each memory location having a width of 8 bits. Such DRAM devices with 128M 8-bit-wide memory locations (actually with a total of  $2^{27}$  or 134,217,728 memory locations with 8 bits each) are identified as having a "128 Mb×8" or "128M× 8-bit" configuration, or as having a depth of 128M and a bit 65 width of 8. Furthermore, certain commercially-available 1-GB memory modules are identified as having a "128M×

2

8-byte" configuration or a " $128M \times 64$ -bit" configuration with a depth of 128M and a width of 8 bytes or 64 bits.

The commercially-available 512-MB (64M×8-byte) memory modules and the 1-GB (128M×8-byte) memory 5 modules described above are typically used in computer systems (e.g., personal computers) which perform graphics applications since such "×8" configurations are compatible with data mask capabilities often used in such graphics applications. Conversely, memory modules with "×4" con-10 figurations are typically used in computer systems such as servers which are not as graphics-intensive. Examples of such commercially available "×4" memory modules include, but are not limited to, 512-MB (128M×4-byte) memory modules comprising eight 512-Mb (128 Mb×4) memory 15 devices.

The DRAM devices of a memory module are generally arranged as ranks or rows of memory, each rank of memory generally having a bit width. For example, a memory module in which each rank of the memory module is 64 bits wide is described as having an " $\times$ 64" organization. Similarly, a memory module having 72-bit-wide ranks is described as having an " $\times$ 72" organization.

The memory capacity of a memory module increases with the number of memory devices. The number of memory devices of a memory module can be increased by increasing the number of memory devices per rank or by increasing the number of ranks. For example, a memory module with four ranks has double the memory capacity of a memory module with two ranks and four times the memory capacity of a memory module with one rank. Rather than referring to the memory capacity of the memory module, in certain circumstances, the memory density of the memory module is referred to instead.

During operation, the ranks of a memory module are selected or activated by control signals that are received from the processor. Examples of such control signals include, but are not limited to, rank-select signals, also called chip-select signals. Most computer and server systems support one-rank and two-rank memory modules. By only supporting one-rank and two-rank memory modules, the memory density that can be incorporated in each memory slot is limited.

### SUMMARY OF THE INVENTION

In certain embodiments, a memory module is connectable to a computer system. The memory module comprises a printed circuit board, a plurality of memory devices coupled to the printed circuit board, and a logic element coupled to the printed circuit board. The plurality of memory devices has a first number of memory devices. The logic element receives a set of input control signals from the computer system. The set of input control signals corresponds to a second number of memory devices smaller than the first number of memory devices. The logic element generates a set of output control signals in response to the set of input control signals. The set of output control signals corresponds to the first number of memory devices.

In certain embodiments, a method utilizes a memory module in a computer system. The method comprises coupling the memory module to the computer system. The memory module comprises a plurality of memory devices arranged in a first number of ranks. The method further comprises inputting a first set of control signals to the memory module. The first set of control signals corresponds to a second number of ranks smaller than the first number of ranks. The method further comprises generating a second set

of control signals in response to the first set of control signals. The second set of control signals corresponds to the first number of ranks.

In certain embodiments, a memory module is connectable to a computer system. The memory module comprises a 5 plurality of memory devices arranged in a first number of ranks. The memory module comprises means for coupling the memory module to the computer system. The memory module further comprises means for inputting a first set of control signals to the memory module. The first set of 10 control signals corresponds to a second number of ranks smaller than the first number of ranks. The memory module further comprises means for generating a second set of control signals in response to the first set of control signals. The second set of control signals corresponds to the first 15 number of ranks.

In certain embodiments, a memory module is connectable to a computer system. The memory module comprises a first memory device having a first data signal line and a first data strobe signal line. The memory module further comprises a 20 applied to the two DQS pins due to non-simultaneous second memory device having a second data signal line and a second data strobe signal line. The memory module further comprises a common data signal line connectable to the computer system. The memory module further comprises an isolation device electrically coupled to the first data signal 25 line, to the second data signal line, and to the common data signal line. The isolation device selectively alternates between electrically coupling the first data signal line to the common data signal line and electrically coupling the second data signal line to the common data signal line.

### BRIEF DESCRIPTION OF THE DRAWINGS

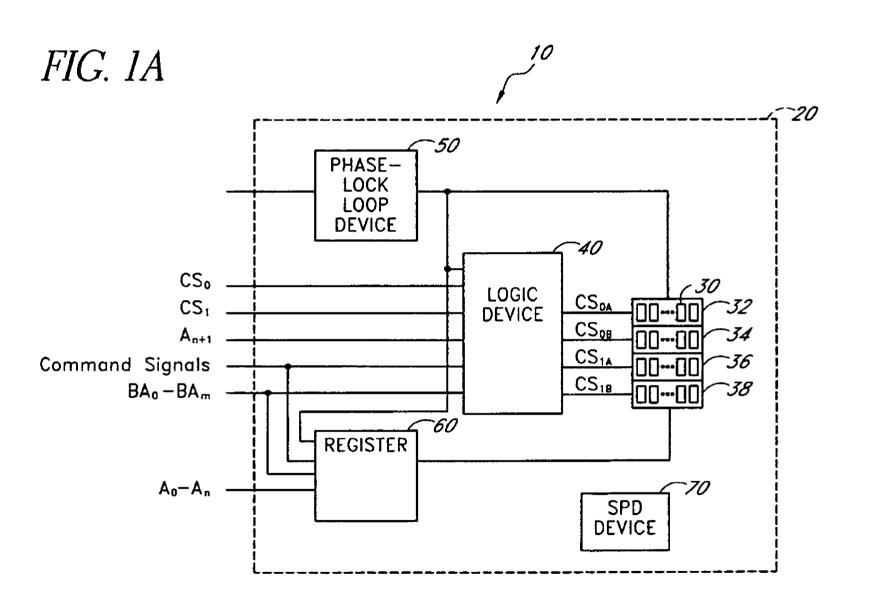

FIG. 1A schematically illustrates an exemplary memory module with four ranks of memory devices compatible with 35 embodiment of a memory module in which a first resistor certain embodiments described herein.

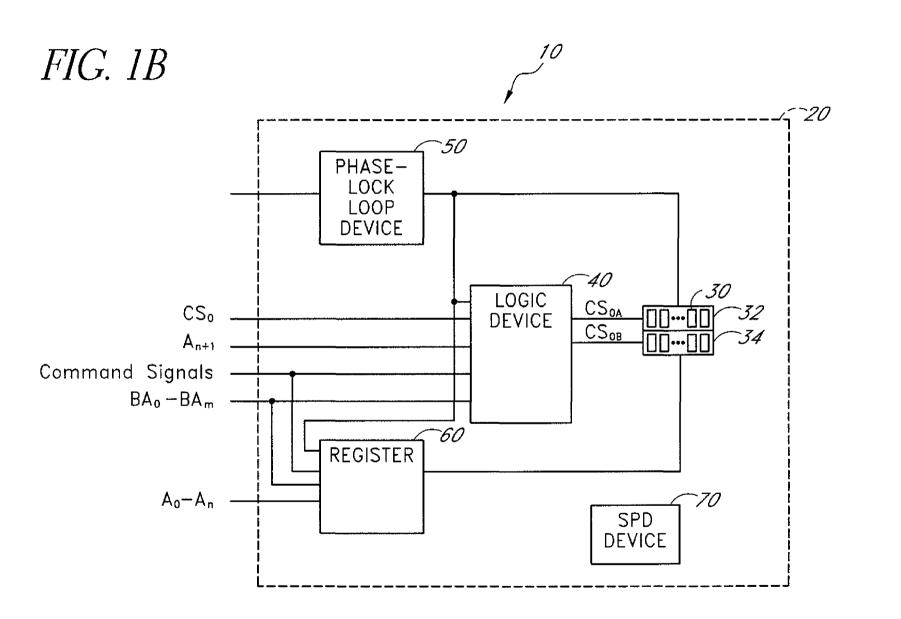

FIG. 1B schematically illustrates an exemplary memory module with two ranks of memory devices compatible with certain embodiments described herein.

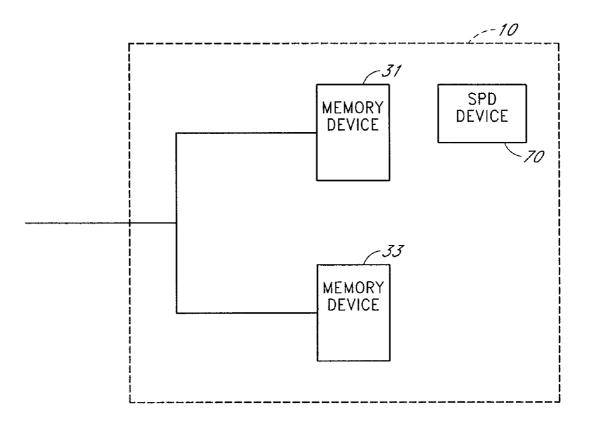

FIG. 1C schematically illustrates another exemplary 40 memory module in accordance with certain embodiments described herein.

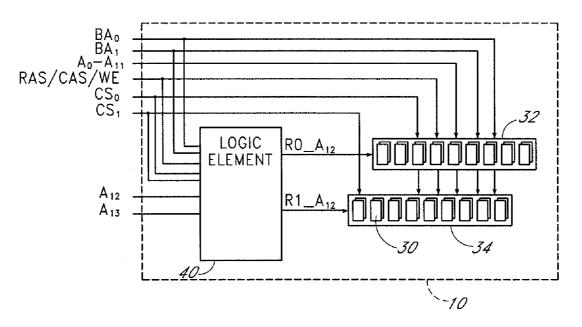

FIG. 2A schematically illustrates an exemplary memory module which doubles the rank density in accordance with certain embodiments described herein.

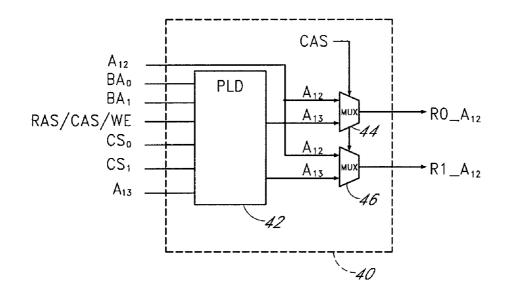

FIG. 2B schematically illustrates an exemplary logic element compatible with embodiments described herein.

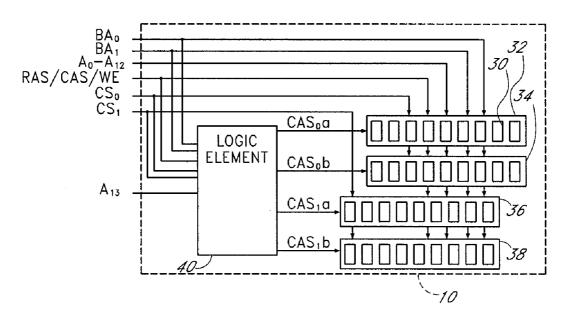

FIG. 3A schematically illustrates an exemplary memory module which doubles number of ranks in accordance with certain embodiments described herein.

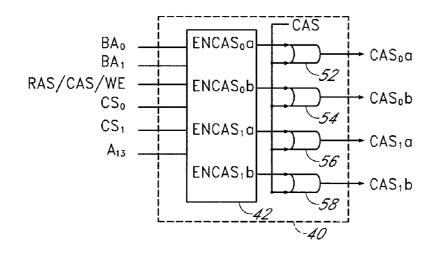

FIG. 3B schematically illustrates an exemplary logic element compatible with embodiments described herein.

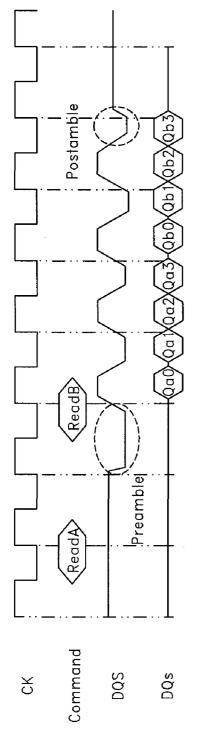

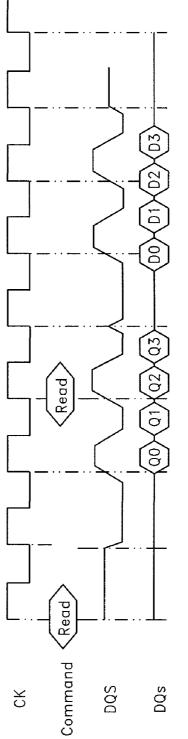

FIG. 4A shows an exemplary timing diagram of a gapless read burst for a back-to-back adjacent read condition from one memory device. 55

FIG. 4B shows an exemplary timing diagram with an extra clock cycle between successive read commands issued to different memory devices for successive read accesses from different memory devices.

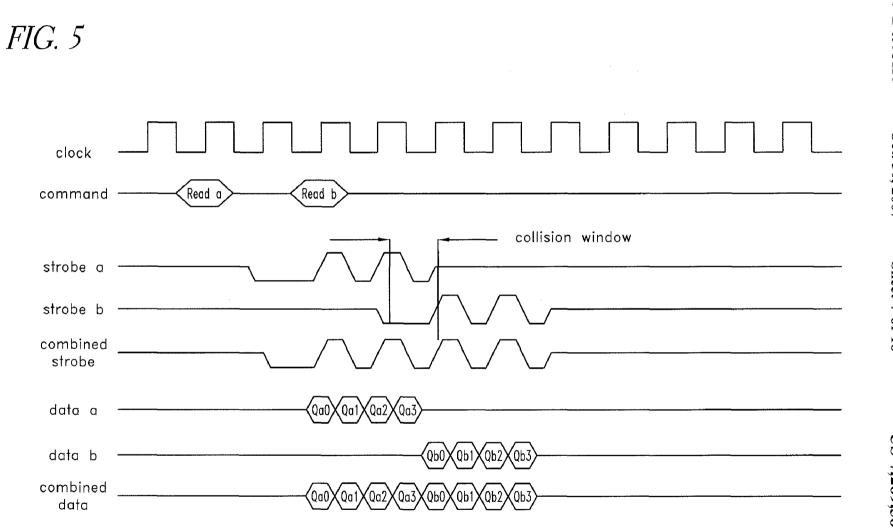

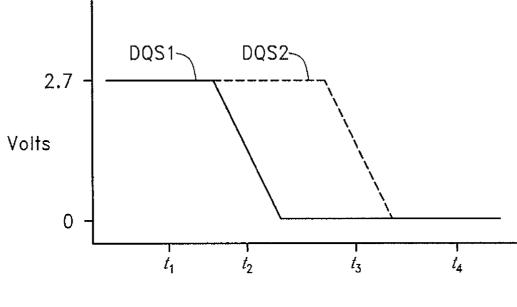

FIG. 5 shows an exemplary timing diagram in which the 60 last data strobe of memory device "a" collides with the pre-amble time interval of the data strobe of memory device "b."

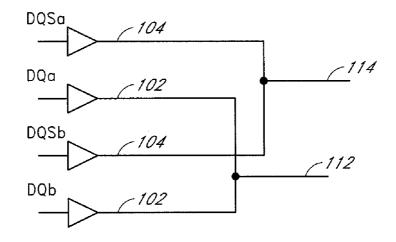

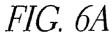

FIG. 6A schematically illustrates a circuit diagram of a conventional memory module showing the interconnections 65 between the DQ data signal lines of two memory devices and their DQS data strobe signal lines.

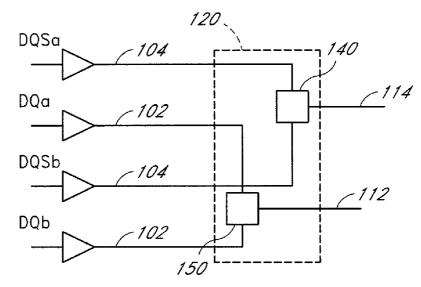

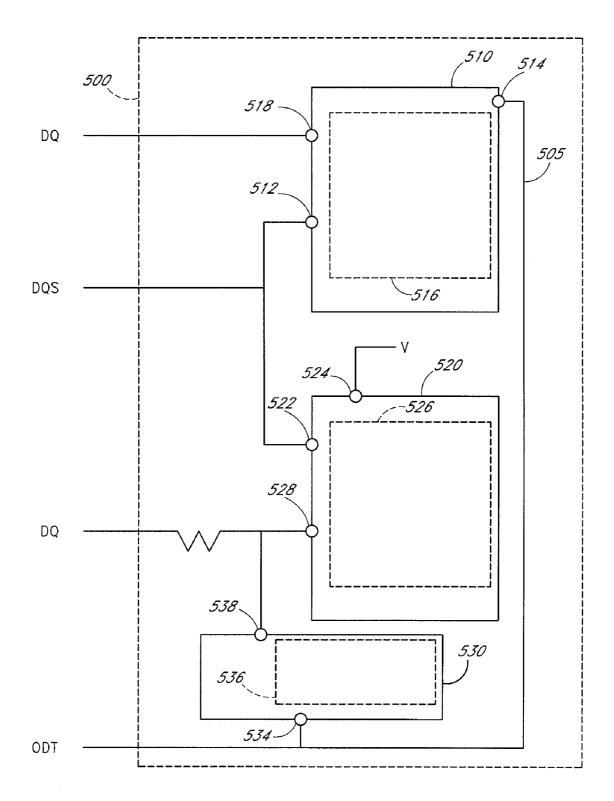

FIG. 6B schematically illustrates a circuit diagram of an exemplary memory module comprising an isolation device in accordance with certain embodiments described herein.

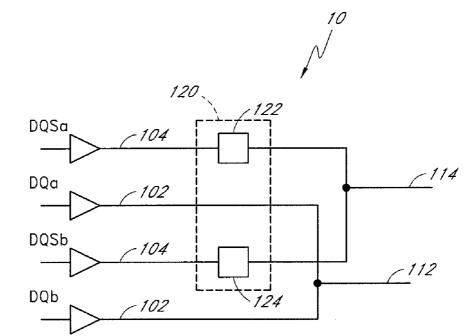

FIG. 6C schematically illustrates an isolation device comprising a logic element which multiplexes the DQS data strobe signal lines from one another.

FIG. 6D schematically illustrates an isolation device which multiplexes the DQS data strobe signal lines from one another and which multiplexes the DQ data signal lines from one another.

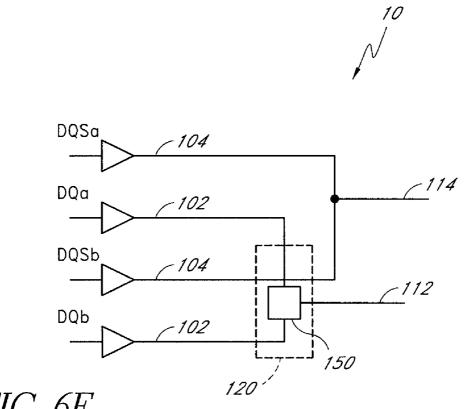

FIG. 6E schematically illustrates an isolation device which comprises the logic element on the DQ data signal lines but not a corresponding logic element on the DQS data strobe signal lines.

FIG. 7 schematically illustrates an exemplary memory module in which a data strobe (DQS) pin of a first memory device is electrically connected to a DQS pin of a second memory device while both DQS pins are active.

FIG. 8 is an exemplary timing diagram of the voltages switching.

FIG. 9 schematically illustrates another exemplary memory module in which a DQS pin of a first memory device is connected to a DQS pin of a second memory device.

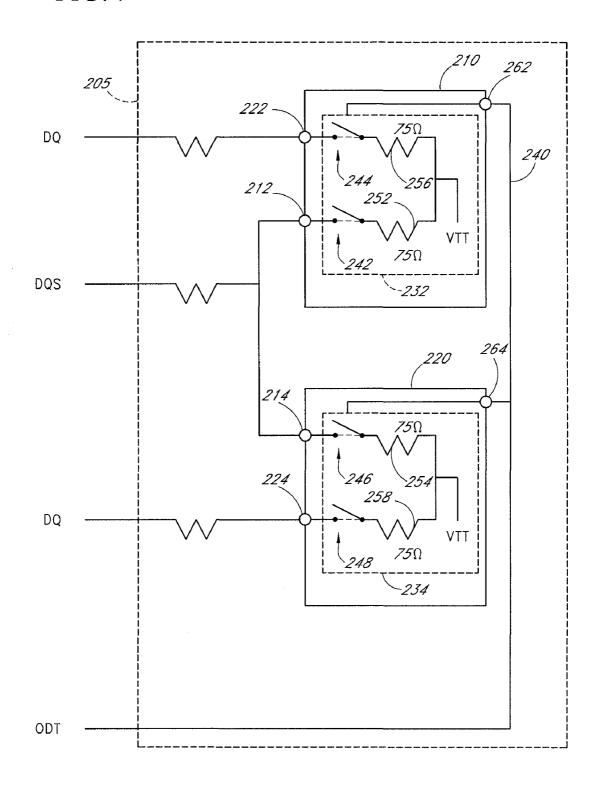

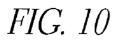

FIG. 10 schematically illustrates an exemplary memory module in accordance with certain embodiments described herein.

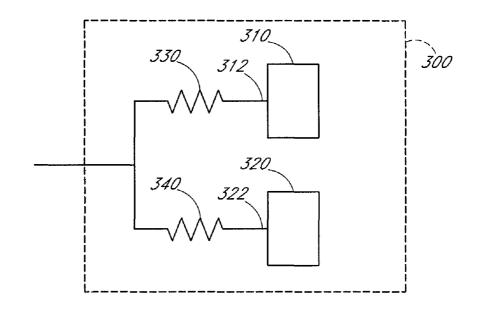

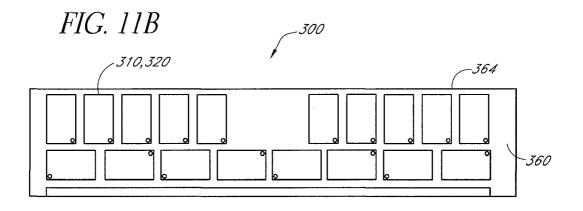

FIGS. 11A and 11B schematically illustrate a first side and 30 a second side, respectively, of a memory module with eighteen 64M×4 bit, DDR-1 SDRAM FBGA memory devices on each side of a 184-pin glass-epoxy printed circuit board.

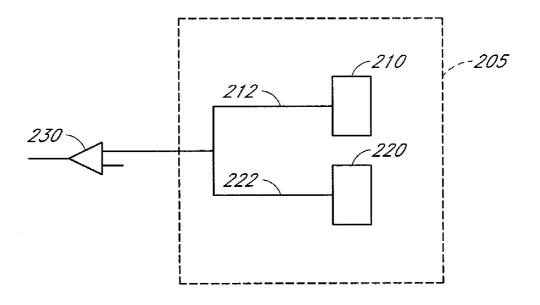

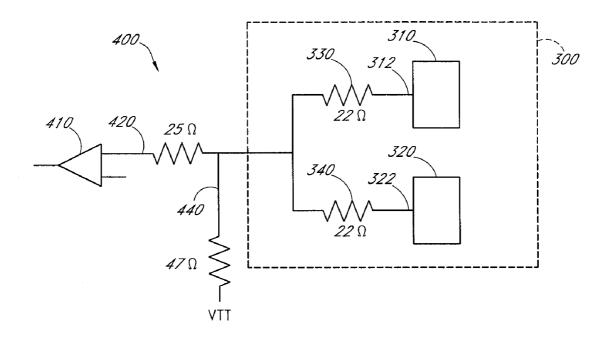

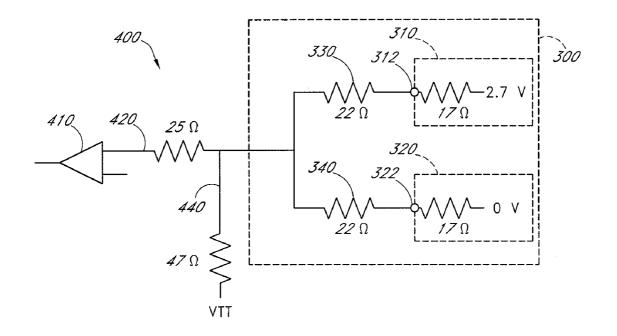

FIGS. 12A and 12B schematically illustrate an exemplary and a second resistor are used to reduce the current flow between the first DQS pin and the second DQS pin.

FIG. 13 schematically illustrates another exemplary memory module compatible with certain embodiments described herein.

FIG. 14 schematically illustrates a particular embodiment of the memory module schematically illustrated by FIG. 13.

### DETAILED DESCRIPTION OF EXEMPLARY EMBODIMENTS

Most high-density memory modules are currently built with 512-Megabit ("512-Mb") memory devices wherein each memory device has a 64M×8-bit configuration. For 50 example, a 1-Gigabyte ("1-GB") memory module with error checking capabilities can be fabricated using eighteen such 512-Mb memory devices. Alternatively, it can be economically advantageous to fabricate a 1-GB memory module using lower-density memory devices and doubling the number of memory devices used to produce the desired word width. For example, by fabricating a 1-GB memory module using thirty-six 256-Mb memory devices with 64M×4-bit configuration, the cost of the resulting 1-GB memory module can be reduced since the unit cost of each 256-Mb memory device is typically lower than one-half the unit cost of each 512-Mb memory device. The cost savings can be significant, even though twice as many 256-Mb memory devices are used in place of the 512-Mb memory devices.

Market pricing factors for DRAM devices are such that higher-density DRAM devices (e.g., 1-Gb DRAM devices) are much more than twice the price of lower-density DRAM devices (e.g., 512-Mb DRAM devices). In other words, the

60

price per bit ratio of the higher-density DRAM devices is greater than that of the lower-density DRAM devices. This pricing difference often lasts for months or even years after the introduction of the higher-density DRAM devices, until volume production factors reduce the costs of the newer 5 higher-density DRAM devices. Thus, when the cost of a higher-density DRAM device is more than the cost of two lower-density DRAM devices, there is an economic incentive for utilizing pairs of the lower-density DRAM devices to replace individual higher-density DRAM devices.

FIG. 1A schematically illustrates an exemplary memory module 10 compatible with certain embodiments described herein. The memory module 10 is connectable to a computer system (not shown). The memory module 10 comprises a printed circuit board 20 and a plurality of memory devices 15 30 coupled to the printed circuit board 20. The plurality of memory devices 30 has a first number of memory devices. The memory module 10 further comprises a logic element 40 coupled to the printed circuit board 20. The logic element **40** receives a set of input control signals from the computer 20 system. The set of input control signals correspond to a second number of memory devices smaller than the first number of memory devices. The logic element 40 generates a set of output control signals in response to the set of input control signals. The set of output control signals corresponds 25 to the first number of memory devices.

In certain embodiments, as schematically illustrated in FIG. 1A, the memory module 10 further comprises a phaselock loop device 50 coupled to the printed circuit board 20 and a register 60 coupled to the printed circuit board 20. In 30 certain embodiments, the phase-lock loop device 50 and the register 60 are each mounted on the printed circuit board 20. In response to signals received from the computer system, the phase-lock loop device 50 transmits clock signals to the plurality of memory devices 30, the logic element 40, and 35 the register 60. The register 60 receives and buffers a plurality of control signals, including address signals (e.g., bank address signals, row address signals, column address signals, gated column address strobe signals, chip-select signals), and transmits corresponding signals to the appro- 40 priate memory devices 30. In certain embodiments, the register 60 comprises a plurality of register devices. While the phase-lock loop device 50, the register 60, and the logic element 40 are described herein in certain embodiments as being separate components, in certain other embodiments, 45 two or more of the phase-lock loop device 50, the register 60, and the logic element 40 are portions of a single component. Persons skilled in the art are able to select a phase-lock loop device 50 and a register 60 compatible with embodiments described herein.

In certain embodiments, the memory module 10 further comprises electrical components which are electrically coupled to one another and are surface-mounted or embedded on the printed circuit board 20. These electrical components can include, but are not limited to, electrical con- 55 duits, resistors, capacitors, inductors, and transistors. In certain embodiments, at least some of these electrical components are discrete, while in other certain embodiments, at least some of these electrical components are constituents of one or more integrated circuits.

Various types of memory modules 10 are compatible with embodiments described herein. For example, memory modules 10 having memory capacities of 512-MB, 1-GB, 2-GB, 4-GB, 8-GB, as well as other capacities, are compatible with embodiments described herein. In addition, memory mod- 65 ules 10 having widths of 4 bytes, 8 bytes, 16 bytes, 32 bytes, or 32 bits, 64 bits, 128 bits, 256 bits, as well as other widths

6

(in bytes or in bits), are compatible with embodiments described herein. Furthermore, memory modules 10 compatible with embodiments described herein include, but are not limited to, single in-line memory modules (SIMMs), dual in-line memory modules (DIMMs), small-outline DIMMs (SO-DIMMs), unbuffered DIMMs (UDIMMs), registered DIMMs (RDIMMs), fully-buffered DIMM (FB-DIMM), mini-DIMMs, and micro-DIMMs.

In certain embodiments, the printed circuit board 20 is mountable in a module slot of the computer system. The printed circuit board 20 of certain such embodiments has a plurality of edge connections electrically coupled to corresponding contacts of the module slot and to the various components of the memory module 10, thereby providing electrical connections between the computer system and the components of the memory module 10.

Memory devices 30 compatible with embodiments described herein include, but are not limited to, randomaccess memory (RAM), dynamic random-access memory (DRAM), synchronous DRAM (SDRAM), and double-datarate DRAM (e.g., DDR-1, DDR-2, DDR-3). In addition, memory devices 30 having bit widths of 4, 8, 16, 32, as well as other bit widths, are compatible with embodiments described herein. Memory devices 30 compatible with embodiments described herein have packaging which include, but are not limited to, thin small-outline package (TSOP), ball-grid-array (BGA), fine-pitch BGA (FBGA), micro-BGA (µBGA), mini-BGA (mBGA), and chip-scale packaging (CSP). Memory devices 30 compatible with embodiments described herein are available from a number of sources, including but not limited to, Samsung Semiconductor, Inc. of San Jose, Calif., Infineon Technologies AG of San Jose, Calif., and Micron Technology, Inc. of Boise, Id. Persons skilled in the art can select appropriate memory devices 30 in accordance with certain embodiments described herein.

In certain embodiments, the plurality of memory devices 30 are arranged in a first number of ranks. For example, in certain embodiments, the memory devices 30 are arranged in four ranks, as schematically illustrated by FIG. 1A. In other embodiments, the memory devices 30 are arranged in two ranks, as schematically illustrated by FIG. 1B. Other numbers of ranks of the memory devices 30 are also compatible with embodiments described herein.

In certain embodiments, the logic element 40 comprises a programmable-logic device (PLD), an application-specific integrated circuit (ASIC), a field-programmable gate array (FPGA), a custom-designed semiconductor device, or a complex programmable-logic device (CPLD). In certain embodiments, the logic element 40 is a custom device. Sources of logic elements 40 compatible with embodiments described herein include, but are not limited to, Lattice Semiconductor Corporation of Hillsboro, Oreg., Altera Corporation of San Jose, Calif., and Xilinx Incorporated of San Jose, Calif. In certain embodiments, the logic element 40 comprises various discrete electrical elements, while in certain other embodiments, the logic element 40 comprises one or more integrated circuits. Persons skilled in the art can select an appropriate logic element 40 in accordance with certain embodiments described herein.

As schematically illustrated by FIGS. 1A and 1B, in certain embodiments, the logic element 40 receives a set of input control signals, which includes address signals (e.g., bank address signals, row address signals, column address signals, gated column address strobe signals, chip-select

signals) and command signals (e.g., refresh, precharge) from the computer system. In response to the set of input control signals, the logic element **40** generates a set of output control signals which includes address signals and command signals.

In certain embodiments, the set of output control signals corresponds to a first number of ranks in which the plurality of memory devices 30 of the memory module 10 are arranged, and the set of input control signals corresponds to a second number of ranks per memory module for which the computer system is configured. The second number of ranks in certain embodiments is smaller than the first number of ranks. For example, in the exemplary embodiment as sche-15 matically illustrated by FIG. 1A, the first number of ranks is four while the second number of ranks is two. In the exemplary embodiment of FIG. 1B, the first number of ranks is two while the second number of ranks is one. Thus, in certain embodiments, even though the memory module 10 actually has the first number of ranks of memory devices 30, the memory module 10 simulates a virtual memory module by operating as having the second number of ranks of memory devices 30. In certain embodiments, the memory module 10 simulates a virtual memory module when the 25 number of memory devices 30 of the memory module 10 is larger than the number of memory devices 30 per memory module for which the computer system is configured to utilize.

In certain embodiments, the computer system is configured for a number of ranks per memory module which is smaller than the number of ranks in which the memory devices **30** of the memory module **10** are arranged. In certain such embodiments, the computer system is configured for two ranks of memory per memory module (providing two chip-select signals  $CS_0$ ,  $CS_1$ ) and the plurality of memory modules **30** of the memory module **10** are arranged in four ranks, as schematically illustrated by FIG. **1A**. In certain other such embodiments, the computer system is configured for one rank of memory per memory module (providing one chip-select signal  $CS_0$ ) and the plurality of memory modules **30** of the memory module **10** are arranged in two ranks, as schematically illustrated by FIG. **1B**.

In the exemplary embodiment schematically illustrated by 45 FIG. 1A, the memory module 10 has four ranks of memory devices 30 and the computer system is configured for two ranks of memory devices per memory module. The memory module 10 receives row/column address signals or signal bits  $(A_0 - A_{n+1})$ , bank address signals  $(BA_0 - BA_m)$ , chip-select signals ( $CS_0$  and  $CS_1$ ), and command signals (e.g., refresh, precharge, etc.) from the computer system. The  $A_0$ - $A_n$ row/column address signals are received by the register 60, which buffers these address signals and sends these address signals to the appropriate ranks of memory devices 30. The logic element 40 receives the two chip-select signals ( $CS_0$ ,  $CS_1$ ) and one row/column address signal  $(A_{n+1})$  from the computer system. Both the logic element 40 and the register 60 receive the bank address signals  $(BA_0 - BA_m)$  and at least 60 one command signal (e.g., refresh, precharge, etc.) from the computer system.

### Logic Tables

Table 1 provides a logic table compatible with certain 65 embodiments described herein for the selection among ranks of memory devices **30** using chip-select signals.

TABLE 1

| 5 | State | $CS_0$ | $CS_1$ | $A_{n+1}$ | Command | $CS_{0A}$ | $CS_{0B}$ | $CS_{1A}$ | $CS_{1B}$ |

|---|-------|--------|--------|-----------|---------|-----------|-----------|-----------|-----------|

|   | 1     | 0      | 1      | 0         | Active  | 0         | 1         | 1         | 1         |

|   | 2     | 0      | 1      | 1         | Active  | 1         | 0         | 1         | 1         |

|   | 3     | 0      | 1      | x         | Active  | 0         | 0         | 1         | 1         |

|   | 4     | 1      | 0      | 0         | Active  | 1         | 1         | 0         | 1         |

| 0 | 5     | 1      | 0      | 1         | Active  | 1         | 1         | 1         | 0         |

|   | 6     | 1      | 0      | х         | Active  | 1         | 1         | 0         | 0         |

|   | 7     | 1      | 1      | х         | x       | 1         | 1         | 1         | 1         |

Note:

30

1.  $Cs_0$ ,  $CS_1$ ,  $CS_{0A}$ ,  $CS_{0B}$ ,  $CS_{1A}$ , and  $CS_{1B}$  are active low signals.

2.  $A_{n+1}$  is an active high signal.

3. 'x' is a Don't Care condition.

4. Command involves a number of command signals that define operations such as refresh, precharge, and other operations.

In Logic State 1:  $CS_0$  is active low,  $A_{n+1}$  is non-active, and Command is active.  $CS_{0,A}$  is pulled low, thereby selecting Rank 0.

In Logic State 2:  $CS_0$  is active low,  $A_{n+1}$  is active, and Command is active.  $CS_{0B}$  is pulled low, thereby selecting Rank 1.

In Logic State 3:  $CS_0$  is active low,  $A_{n+1}$  is Don't Care, and Command is active high.  $CS_{0A}$  and  $CS_{0B}$  are pulled low, thereby selecting Ranks 0 and 1.

In Logic State 4:  $CS_1$  is active low,  $A_{n+1}$  is non-active, and Command is active.  $CS_{1A}$  is pulled low, thereby selecting Rank 2.

In Logic State 5:  $CS_1$  is active low,  $A_{n+1}$  is active, and Command is active.  $CS_{1B}$  is pulled low, thereby selecting Rank 3.

In Logic State 6: CS<sub>1</sub> is active low, A<sub>n+1</sub> is Don't Care, 40 and Command is active. CS<sub>1,4</sub> and CS<sub>1,B</sub> are pulled low, thereby selecting Ranks 2 and 3.

In Logic State 7:  $CS_0$  and  $CS_1$  are pulled non-active high, which deselects all ranks, i.e.,  $CS_{0,4}$ ,  $CS_{0,B}$ ,  $CS_{1,4}$ , and  $CS_{1,B}$ are pulled high.

The "Command" column of Table 1 represents the various commands that a memory device (e.g., a DRAM device) can execute, examples of which include, but are not limited to, activation, read, write, precharge, and refresh. In certain embodiments, the command signal is passed through to the selected rank only (e.g., state 4 of Table 1). In such embodiments, the command signal (e.g., read) is sent to only one memory device or the other memory device so that data is supplied from one memory device at a time. In other embodiments, the command signal is passed through to both associated ranks (e.g., state 6 of Table 1). In such embodiments, the command signal (e.g., refresh) is sent to both memory devices to ensure that the memory content of the memory devices remains valid over time. Certain embodiments utilize a logic table such as that of Table 1 to simulate a single memory device from two memory devices by selecting two ranks concurrently.

Table 2 provides a logic table compatible with certain embodiments described herein for the selection among ranks of memory devices **30** using gated CAS signals.

TABLE 2

| CS* | RAS* | CAS* | WE* | Density Bit | A <sub>10</sub> | Command      | CAS0* | CAS1* |

|-----|------|------|-----|-------------|-----------------|--------------|-------|-------|

| 1   | х    | х    | х   | х           | х               | NOP          | х     | х     |

| 0   | 1    | 1    | 1   | х           | х               | NOP          | 1     | 1     |

| 0   | 0    | 1    | 1   | 0           | х               | ACTIVATE     | 1     | 1     |

| 0   | 0    | 1    | 1   | 1           | х               | ACTIVATE     | 1     | 1     |

| 0   | 1    | 0    | 1   | 0           | х               | READ         | 0     | 1     |

| 0   | 1    | 0    | 1   | 1           | х               | READ         | 1     | 0     |

| 0   | 1    | 0    | 0   | 0           | х               | WRITE        | 0     | 1     |

| 0   | 1    | 0    | 0   | 1           | х               | WRITE        | 1     | 0     |

| 0   | 0    | 1    | 0   | 0           | 0               | PRECHARGE    | 1     | 1     |

| 0   | 0    | 1    | 0   | 1           | 0               | PRECHARGE    | 1     | 1     |

| 0   | 0    | 1    | 0   | х           | 1               | PRECHARGE    | 1     | 1     |

| 0   | 0    | 0    | 0   | х           | х               | MODE REG SET | 0     | 0     |

| 0   | 0    | 0    | 1   | х           | х               | REFRESH      | 0     | 0     |

In certain embodiments in which the density bit is a row address bit, for read/write commands, the density bit is the value latched during the activate command for the selected <sup>20</sup> bank.

### Serial-Presence-Detect Device

Memory modules typically include a serial-presence detect (SPD) device **70** (e.g., an electrically-erasable-programmable read-only memory or EEPROM device) comprising data which characterize various attributes of the memory module, including but not limited to, the number of row addresses the number of column addresses, the data width of the memory devices, the number of ranks, the 30 memory density per rank, the number of memory devices, and the memory density per memory device. The SPD device **70** communicates this data to the basic input/output system (BIOS) of the computer system so that the computer system is informed of the memory capacity and the memory 35 configuration available for use and can configure the memory controller properly for maximum reliability and performance.

For example, for a commercially-available 512-MB (64M×8-byte) memory module utilizing eight 512-Mb 40 memory devices each with a 64M×8-bit configuration, the SPD device contains the following SPD data (in appropriate bit fields of these bytes):

- Byte 3: Defines the number of row address bits in the DRAM device in the memory module [13 for the 45 512-Mb memory device].

- Byte 4: Defines the number of column address bits in the DRAM device in the memory module [11 for the 512-Mb memory device].

- Byte 13: Defines the bit width of the primary DRAM <sup>50</sup> device used in the memory module [8 bits for the 512-Mb (64M×8-bit) memory device].

- Byte 14: Defines the bit width of the error checking DRAM device used in the memory module [8 bits for the 512-Mb (64M×8-bit) memory device]. 55

- Byte **17**: Defines the number of banks internal to the DRAM device used in the memory module [4 for the 512-Mb memory device].

In a further example, for a commercially-available 1-GB  $_{60}$  (128M×8-byte) memory module utilizing eight 1-Gb memory devices each with a 128M×8-bit configuration, as described above, the SPD device contains the following SPD data (in appropriate bit fields of these bytes):

Byte **3**: Defines the number of row address bits in the 65 DRAM device in the memory module [14 for the 1-Gb memory device].

- Byte 4: Defines the number of column address bits in the DRAM device in the memory module [11 for the 1-Gb memory device].

- Byte **13**: Defines the bit width of the primary DRAM device used in the memory module [8 bits for the 1-Gb (128M×8-bit) memory device].

- Byte 14: Defines the bit width of the error checking DRAM device used in the memory module [8 bits for the 1-Gb (128M×8-bit) memory device].

- Byte 17: Defines the number of banks internal to the DRAM device used in the memory module [4 for the 1-Gb memory device].

In certain embodiments, the SPD device 70 comprises data which characterize the memory module 10 as having fewer ranks of memory devices than the memory module 10 actually has, with each of these ranks having more memory density. For example, for a memory module 10 compatible with certain embodiments described herein having two ranks of memory devices 30, the SPD device 70 comprises data which characterizes the memory module 10 as having one rank of memory devices with twice the memory density per rank. Similarly, for a memory module 10 compatible with certain embodiments described herein having four ranks of memory devices 30, the SPD device 70 comprises data which characterizes the memory module 10 as having two ranks of memory devices with twice the memory density per rank. In addition, in certain embodiments, the SPD device 70 comprises data which characterize the memory module 10 as having fewer memory devices than the memory module 10 actually has, with each of these memory devices having more memory density per memory device. For example, for a memory module 10 compatible with certain embodiments described herein, the SPD device 70 comprises data which characterizes the memory module 10 as having one-half the number of memory devices that the memory module 10 actually has, with each of these memory devices having twice the memory density per memory device.

FIG. 1C schematically illustrates an exemplary memory module 10 in accordance with certain embodiments described herein. The memory module 10 comprises a pair of substantially identical memory devices 31, 33. Each memory device 31, 33 has a first bit width, a first number of banks of memory locations, a first number of rows of memory locations, and a first number of columns of memory locations. The memory module 10 further comprises an SPD device 70 comprising data that characterizes the pair of memory devices 31, 33. The data characterize the pair of memory devices 31, 33 as a virtual memory device having a second bit width equal to twice the first bit width, a second number of banks of memory locations equal to the first number of banks, a second number of rows of memory locations equal to the first number of rows, and a second number of columns of memory locations equal to the first number of columns.

In certain such embodiments, the SPD device **70** of the memory module **10** is programmed to describe the combined pair of lower-density memory devices **31**, **33** as one virtual or pseudo-higher-density memory device. In an exemplary embodiment, two 512-Mb memory devices, each with a 10 128M×4-bit configuration, are used to simulate one 1-Gb memory device having a 128M×8-bit configuration. The SPD device **70** of the memory module **10** is programmed to describe the pair of 512-Mb memory devices as one virtual or pseudo-1-Gb memory device.

For example, to fabricate a 1-GB (128M×8-byte) memory module, sixteen 512-Mb (128M×4-bit) memory devices can be used. The sixteen 512-Mb (128M×4-bit) memory devices are combined in eight pairs, with each pair serving as a virtual or pseudo-1-Gb (128M×8-bit) memory device. In 20 certain such embodiments, the SPD device **70** contains the following SPD data (in appropriate bit fields of these bytes): Byte **3**: 13 row address bits.

Byte 4: 12 column address bits.

Byte 13: 8 bits wide for the primary virtual 1-Gb (128M× 25 8-bit) memory device.

Byte **14**: 8 bits wide for the error checking virtual 1-Gb (128M×8-bit) memory device.

Byte 17: 4 banks.

In this exemplary embodiment, bytes **3**, **4**, and **17** are 30 programmed to have the same values as they would have for a 512-MB ( $128M\times4$ -byte) memory module utilizing 512-Mb ( $128M\times4$ -bit) memory devices. However, bytes **13** and **14** of the SPD data are programmed to be equal to 8, corresponding to the bit width of the virtual or pseudo-35 higher-density 1-Gb ( $128M\times8$ -bit) memory device, for a total capacity of 1-GB. Thus, the SPD data does not describe the actual-lower-density memory devices, but instead describes the virtual or pseudo-higher-density memory devices. The BIOS accesses the SPD data and recognizes the 40 memory module as having 4 banks of memory locations arranged in  $2^{13}$  rows and  $2^{12}$  columns, with each memory location having a width of 8 bits rather than 4 bits.

In certain embodiments, when such a memory module 10 is inserted in a computer system, the computer system's 45 memory controller then provides to the memory module 10 a set of input control signals which correspond to the number of ranks or the number of memory devices reported by the SPD device 70. For example, placing a two-rank memory module 10 compatible with certain embodiments described 50 herein in a computer system compatible with one-rank memory modules, the SPD device 70 reports to the computer system that the memory module 10 only has one rank. The logic element 40 then receives a set of input control signals corresponding to a single rank from the computer system's 55 memory controller, and generates and transmits a set of output control signals corresponding to two ranks to the appropriate memory devices 30 of the memory module 10. Similarly, when a two-rank memory module 10 compatible with certain embodiments described herein is placed in a 60 computer system compatible with either one- or two-rank memory modules, the SPD device 70 reports to the computer system that the memory module 10 only has one rank. The logic element 40 then receives a set of input control signals corresponding to a single rank from the computer system's 65 memory controller, and generates and transmits a set of output control signals corresponding to two ranks to the

12

appropriate memory devices **30** of the memory module **10**. Furthermore, a four-rank memory module **10** compatible with certain embodiments described herein simulates a two-rank memory module whether the memory module **10** is inserted in a computer system compatible with two-rank memory modules or with two- or four-rank memory modules. Thus, by placing a four-rank memory module **10** compatible with certain embodiments described herein in a module slot that is four-rank-ready, the computer system provides four chip-select signals, but the memory module **10** only uses two of the chip-select signals.

### Memory Density Multiplication

In certain embodiments, two memory devices having a <sup>15</sup> memory density are used to simulate a single memory device having twice the memory density, and an additional address signal bit is used to access the additional memory. Similarly, in certain embodiments, two ranks of memory devices having a memory density are used to simulate a <sup>20</sup> single rank of memory devices having twice the memory density, and an additional address signal bit is used to access the additional memory. As used herein, such simulations of memory devices or ranks of memory devices are termed as "memory density multiplication," and the term "density transition bit" is used to access the additional address signal bit which is used to access the additional address signal bit which is used to access the additional address signal bit which is used to access the additional memory.

In certain embodiments utilizing memory density multiplication embodiments, the memory module **10** can have various types of memory devices **30** (e.g., DDR1, DDR2, DDR3, and beyond). The logic element **40** of certain such embodiments utilizes implied translation logic equations having variations depending on whether the density transition bit is a row, column, or internal bank address bit. In addition, the translation logic equations of certain embodiments vary depending on the type of memory module **10** (e.g., UDIMM, RDIMM, FBDIMM, etc.). Furthermore, in certain embodiments, the translation logic equations vary depending on whether the implementation multiplies memory devices per rank or multiplies the number of ranks per memory module.

Table 3A provides the numbers of rows and columns for DDR-1 memory devices, as specified by JEDEC standard JESD79D, "Double Data Rate (DDR) SDRAM Specification," published February 2004, and incorporated in its entirety by reference herein.

TABLE 3A

|                                                       | 128-Mb | 256-Mb | 512-Mb | 1-Gb |

|-------------------------------------------------------|--------|--------|--------|------|

| Number of banks                                       | 4      | 4      | 4      | 4    |

| Number of row address bits                            | 12     | 13     | 13     | 14   |

| Number of column address bits for "×4" configuration  | 11     | 11     | 12     | 12   |

| Number of column address bits for "×8" configuration  | 10     | 10     | 11     | 11   |

| Number of column address bits for "x16" configuration | 9      | 9      | 10     | 10   |

As described by Table 3A, 512-Mb ( $128M\times4$ -bit) DRAM devices have  $2^{13}$  rows and  $2^{12}$  columns of memory locations, while 1-Gb ( $128M\times8$ -bit) DRAM devices have  $2^{14}$  rows and  $2^{11}$  columns of memory locations. Because of the differences in the number of rows and the number of columns for the two types of memory devices, complex address translation procedures and structures would typically be needed to fabricate a 1-GB ( $128M\times8$ -bit) DRAM devices.

Table 3B shows the device configurations as a function of memory density for DDR2 memory devices.

TABLE 3B

|       |    | Number of<br>Rows | Number of<br>Columns | Number of<br>Internal Banks | Page Size<br>(×4s or ×8s) |

|-------|----|-------------------|----------------------|-----------------------------|---------------------------|

| 256 ] | Mb | 13                | 10                   | 4                           | 1 KB                      |

| 512   | Mb | 14                | 10                   | 4                           | 1 KB                      |

| 1 (   | Gb | 14                | 10                   | 8                           | 1 KB                      |

| 2     | Gb | 15                | 10                   | 8                           | 1  KB                     |

| 4 (   | Gb | to be             | to be                | 8                           | 1 KB                      |

|       |    | determined        | determined           |                             |                           |

Table 4 lists the corresponding density transition bit for the density transitions between the DDR2 memory densities of 20 Table 3B.

TABLE 4

| Density Transition                 | Density Transition Bit       | 25 |

|------------------------------------|------------------------------|----|

| 256 Mb to 512 Mb<br>512 Mb to 1 Gb | $A_{13}$ BA <sub>2</sub>     | -  |

| 1 Gb to 2 Gb<br>2 Gb to 4 Gb       | $A_{14}$<br>to be determined |    |

| 2 00 10 4 00                       |                              | 30 |

Because the standard memory configuration of 4-Gb DDR2 SDRAM modules is not yet determined by the appropriate standards-setting organization, Tables 3B and 4 have "to be determined" in the appropriate table entries.

In certain embodiments, the logic translation equations are programmed in the logic element 40 by hardware, while in certain other embodiments, the logic translation equations <sup>10</sup> are programmed in the logic element **40** by software. Examples 1 and 2 provide exemplary sections of Verilog code compatible with certain embodiments described herein. As described more fully below, the code of Examples 1 and 2 includes logic to reduce potential problems due to "backto-back adjacent read commands which cross memory device boundaries or "BBARX." Persons skilled in the art are able to provide additional logic translation equations compatible with embodiments described herein.

An exemplary section of Verilog code compatible with memory density multiplication from 512 Mb to 1 Gb using DDR2 memory devices with the BA2 density transition bit 25 is listed below in Example 1. The exemplary code of Example 1 corresponds to a logic element 40 which receives one chip-select signal from the computer system and which generates two chip-select signals.

### EXAMPLE 1

| always @(posedge clk_in)                                             |                            |

|----------------------------------------------------------------------|----------------------------|

| begin                                                                |                            |

| $rs0N_R \ll rs0_in_N;$ // cs0                                        |                            |

| rasN_R <= ras_in_N;                                                  |                            |

| $casN_R \le cas_in_N;$                                               |                            |

| $weN_R \le we_in_N;$                                                 |                            |

| end                                                                  |                            |

| // Gated Chip Selects                                                |                            |

| assign $pcs0a_1 = (\sim rs0_in_N \& \sim ras_in_N \& \sim cas_in_N)$ | // ref,md reg set          |

| $(\sim rs0_in_N \& ras_in_N \& cas_in_N)$                            | // ref exit, pwr dn        |

| (~rs0_in_N & ~ras_in_N & cas_in_N & ~we_in_N & a10_in)               | // pchg all                |

| (~rs0_in_N & ~ras_in_N & cas_in_N & ~we_in_N & ~a10_in &             | ~ba2_in)// pchg single bnk |

| (~rs0_in_N & ~ras_in_N & cas_in_N & we_in_N & ~ba2_in                | ) // activate              |

| (~rs0_in_N & ras_in_N & ~cas_in_N & ~ba2_in)                         | // xfr                     |

| ;                                                                    |                            |

| assign                                                               | // ref,md reg set          |

| (~rs0_in_N & ras_in_N & cas_in_N)                                    | // ref exit, pwr dn        |

| (~rs0_in_N & ~ras_in_N & cas_in_N & ~we_in_N & a10_in)               | // pchg all                |

| (~rs0_in_N & ~ras_in_N & cas_in_N & ~we_in_N & ~a10_in &             | ba2_in)// pchg single bnk  |

| (~rs0_in_N & ~ras_in_N & cas_in_N & we_in_N & ba2_in)                | // activate                |

| (~rs0_in_N & ras_in_N & ~cas_in_N & ba2_in)                          | // xfr                     |

| ;                                                                    |                            |

| //                                                                   |                            |

| always @(posedge_clk_in)                                             |                            |

| begin                                                                |                            |

| a4_r <= a4_in ,                                                      |                            |

| a5_r <= a5_in;                                                       |                            |

| $a6_r \ll a6_in;$                                                    |                            |

| $a10_r <= a10_in;$                                                   |                            |

| $ba0_r \ll ba0_in$ ;                                                 |                            |

| $bal_r \ll bal_in;$                                                  |                            |

| ba2_r <= ba2_in;                                                     |                            |

| q_mrs_cmd_cyc1 <= q_mrs_cmd ;<br>end                                 |                            |

|                                                                      |                            |

|                                                                      |                            |

| // determine the cas latency                                         |                            |

|                                                                      |                            |

| assign $q_mrs\_cmd\_r = (!rasN\_R \& !casN\_R \& !weN\_R)$           |                            |

| & !rs0N_R                                                            |                            |

|                                                                      |                            |

|                  | -continued                                                                 |                                                    |

|------------------|----------------------------------------------------------------------------|----------------------------------------------------|

|                  | ba0_r & !ba1_r)                                                            |                                                    |

| if (~re          | // md reg set cmd<br>@(posedge clk_in)<br>set_N) // lmr                    |                                                    |

| else if          | <= l 'b1 ;<br>(q_mrs_cmd_cyc1) // load mode reg cmd                        |                                                    |

|                  | <= (~a6_r & a5_r & a4_r );                                                 |                                                    |

|                  | @(posedge clk_in)                                                          |                                                    |

| cl2              | <pre>set_N) // reset &lt;= 1 'b0 ;</pre>                                   |                                                    |

| else if<br>begin | (q_mrs_cmd_cyc1) // load mode reg cmd                                      |                                                    |

| cl2<br>end       | <= (~a6_r & a5_r & ~a4_r ) ;                                               |                                                    |

| if (~re          | <pre>@(posedge clk_in) set_N) // reset</pre>                               |                                                    |

|                  | <= 1 'b0 ;<br>(q_mrs_cmd_cyc1) // load mode reg cmd                        |                                                    |

| begin<br>cl4     | <= (a6_r & ~a5_r & ~a4_r );                                                |                                                    |

|                  | @(posedge clk_in)                                                          |                                                    |

| else if          | set_N) cl5 <= l 'b0 ;<br>(q_mrs_cmd_cyc1) // load mode reg cmd             |                                                    |

|                  | <= (a6_r & ~a5_r & a4_r );                                                 |                                                    |

| end<br>assign    | pre_cyc2_enfet = (wr_cmd_cyc1 & acs_cyc1 & cl3)                            | // wr brst cl3 preamble                            |

| assign           | ;<br>pre_cyc3_enfet = (rd_cmd_cyc2 & cl3)                                  | // rd brst cl3 preamble                            |

|                  | (wr_cmd_cyc2 & cl3)<br>  (wr_cmd_cyc2 & cl4)                               | // wr brst cl3 1st pair<br>// wr brst cl4 preamble |

| assign           | ;<br>pre_cyc4_enfet = (wr_cmd_cyc3 & cl3)<br>  (wr_cmd_cyc3 & cl4)         | // wr brst cl3 2nd pair<br>// wr brst cl4 1st pair |

|                  | (rd_cmd_cyc3 & cl3)<br>  (rd_cmd_cyc3 & cl4)                               | // rd brst cl3 1st pair<br>// rd brst cl4 preamble |

| assign           | <pre>,<br/>pre_cyc5_enfet = (rd_cmd_cyc4 &amp; cl3)</pre>                  | // rd brst cl3 2nd pair<br>// wr brst cl4 2nd pair |

|                  | (rd_cmd_cyc4 & cl4)<br>;                                                   | // rd brst cl4 1st pair                            |

| // dq<br>assign  | pre_dq_cyc = pre_cyc2_enfet                                                |                                                    |

|                  | pre_cyc3_enfet<br>  pre_cyc4_enfet                                         |                                                    |

|                  | pre_cyc5_enfet<br>;                                                        |                                                    |

| assign           | pre_dq_ncyc = enfet_cyc2<br>  enfet_cyc3                                   |                                                    |

|                  | enfet_cyc4<br>  enfet_cyc5                                                 |                                                    |

| // dqs           | ;                                                                          |                                                    |

| assign           | pre_dqsa_cyc = (pre_cyc2_enfet & ~ba2_r)<br>  (pre_cyc3_enfet & ~ba2_cyc2) |                                                    |

|                  | (pre_cyc4_enfet & ~ba2_cyc3)<br>  (pre_cyc5_enfet & ~ba2_cyc4)             |                                                    |

| assign           | ;<br>pre_dqsb_cyc = (pre_cyc2_enfet & ba2_r)                               |                                                    |

|                  | (pre_cyc3_enfet & ba2_cyc2)<br>  (pre_cyc4_enfet & ba2_cyc3)               |                                                    |

|                  | (pre_cyc5_enfet & ba2_cyc4)                                                |                                                    |

| assign           | pre_dqsa_ncyc = (enfet_cyc2 & ~ba2_cyc2)<br>  (enfet_cyc3 & ~ba2_cyc3)     |                                                    |

|                  | (enfet_cyc4 & ~ba2_cyc4)<br>  (enfet_cyc5 & ~ba2_cyc5)                     |                                                    |

| assign           | ;<br>pre_dqsb_ncyc = (enfet_cyc2 & ba2_cyc2)                               |                                                    |

|                  | (enfet_cyc3 & ba2_cyc3)<br>  (enfet_cyc4 & ba2_cyc4)                       |                                                    |

|                  | (enfet_cyc5 & ba2_cyc5)<br>;<br>@/maadaa allt_in)                          |                                                    |

| begin            | <pre>@(posedge clk_in)</pre>                                               |                                                    |

| acs_             | _cyc2 <= acs_cyc1 ; // cs active                                           |                                                    |

|                  |                                                                            |                                                    |

| -con                                                     | tinued |

|----------------------------------------------------------|--------|

| $ba2\_cyc2 \le ba2\_r$ ;                                 |        |

| $ba2\_cyc3 \le ba2\_cyc2$ ;                              |        |

| $ba2\_cyc4 \le ba2\_cyc3$ ;                              |        |

| $ba2\_cyc5 \le ba2\_cyc4$ ;                              |        |

| rd_cmd_cyc2 <= rd_cmd_cyc1 & acs_cyc1;                   |        |

| rd_cmd_cyc3 <= rd_cmd_cyc2 ;                             |        |

| rd_cmd_cyc4 <= rd_cmd_cyc3 ;                             |        |

| $rd\_cmd\_cyc5 <= rd\_cmd\_cyc4;$                        |        |

| rd_cmd_cyc6 <= rd_cmd_cyc5 ;                             |        |

| rd_cmd_cyc7 <= rd_cmd_cyc6 ;                             |        |

| <pre>wr_cmd_cyc2 &lt;= wr_cmd_cyc1 &amp; acs_cyc1;</pre> |        |

| <pre>wr_cmd_cyc3 &lt;= wr_cmd_cyc2 ;</pre>               |        |

| wr_cmd_cyc4 <= wr_cmd_cyc3;                              |        |

| <pre>wr_cmd_cyc5 &lt;= wr_cmd_cyc4 ;</pre>               |        |

| end                                                      |        |

| always @(negedge clk_in)                                 |        |

| begin                                                    |        |

| dq_ncyc <= dq_cyc;                                       |        |

| $dqs\_ncyc\_a \le dqs\_cyc\_a;$                          |        |

| dqs_ncyc_b <= dqs_cyc_b;<br>end                          |        |

| // DQ FET enables                                        |        |

| assign $enq_fet1 = dq_cyc   dq_ncyc$                     |        |

| assign $enq_fet2 = dq_cyc   dq_ncyc ;$                   | ,      |

| assign $enq_fet3 = dq_cyc   dq_ncyc$                     |        |

| assign $enq_fet4 = dq_cyc   dq_ncyc ;$                   | ,      |

| assign $enq_fet5 = dq_cyc \mid dq_ncyc$ ;                |        |

| // DQS FET enables                                       |        |

| assign $ens_fet1a = dqs_cvc_a   dqs_ncvc_a$              | :      |

| assign $ens_fet2a = dqs_cvc_a   dqs_ncvc_a$              | :      |

| assign $ens_fet3a = dqs_cyc_a   dqs_ncyc_a$              | ,      |

| assign $ens_fet1b = dqs_cyc_b   dqs_ncyc_b$              | ,      |

| assign $ens\_fet2b = dqs\_cyc\_b   dqs\_ncyc\_b$         | ;      |

| assign $ens\_fet3b = dqs\_cyc\_b   dqs\_ncyc\_b$         | ;      |

Another exemplary section of Verilog code compatible with memory density multiplication from 256 Mb to 512 Mb using DDR2 memory devices and gated CAS signals with <sup>35</sup> the row  $A_{13}$  density transition bit is listed below in Example 2. The exemplary code of Example 2 corresponds to a logic element **40** which receives one gated CAS signal from the computer system and which generates two gated CAS signals. <sup>40</sup>

### EXAMPLE 2

```

// latched a13 flags cs0, banks 0-3

always @(posedge clk_in) if (actv_cmd_R & ~rs0N_R & ~bnk1_R & ~bnk0_R) // activate

begin

l_a13_00 <= a13_r;

end

always @(posedge clk_in)

if (actv_cmd_R & ~rs0N_R & ~bnk1_R & bnk0_R) // activate

begin

l_a13_01 <= a13_r ;

end

always @(posedge clk_in)

if (actv_cmd_R & ~rs0N_R & bnk1_R & ~bnk0_R) // activate

begin

l_a13_10 \le a13_r;

end

always @(posedge clk_in)

if (actv_cmd_R & ~rs0N_R & bnk1_R & bnk0_R) // activate

begin

l_a13_11 <= a13_r;

end

\ensuremath{\textit{//}}\xspace gated cas

assign cas_i = \sim(casN_R);

assign cas0_o = ( \simrasN_R & cas_i)

```

-continued

| ( rasN\_R & ~l\_a13\_00 & ~bnk1\_R & ~bnk0\_R & cas\_i) ( rasN\_R & ~l\_a13\_01 & ~bnk1\_R & bnk0\_R & cas\_i)  $|(rasN_R \& \sim | a13_10 \& bnk1_R \& \sim bnk0_R \& cas_i)$ | ( rasN\_R & ~l\_a13\_11 & bnk1\_R & bnk0\_R & cas\_i) assign cas1\_o = ( ~rasN\_R & cas\_i) | ( rasN\_R & 1\_a13\_00 & ~bnk1\_R & ~bnk0\_R & cas\_i) & ~bnk1\_R & bnk0\_R & cas\_i)  $\parallel$  ( <code>rasN\_R & l\_a13\_01</code> & bnk1\_R & ~bnk0\_R & cas i) | ( rasN\_R & 1\_a13\_10 | (rasN\_R & l\_a13\_11 & bnk1\_R & bnk0\_R & cas\_i)  $pcas_0_N = \sim cas0_o;$ assign  $pcas_1_N = \sim cas1_0;$ assign assign rd0\_o\_R1 = rasN\_R & cas0\_o & weN\_R & ~rs0N\_R; // rnk0 rd cmd cyc assign rd1\_o\_R1 = rasN\_R & cas1\_o & weN\_R & ~rs0N\_R; // rnk1 rd cmd cyc assign wr0\_o\_R1 = rasN\_R & cas0\_o & ~weN\_R & ~rs0N\_R; // rnk0 wr cmd cyc assign wr1\_o\_R1 = rasN\_R & cas1\_o & ~weN\_R & ~rs0N\_R ; // rnk1 wr cmd cyc always @(posedge clk\_in) begin  $rd0_0_R2 \le rd0_0_R1$ ; rd0\_o\_R3 <= rd0\_o\_R2; rd0\_o\_R4 <= rd0\_o\_R3; rd0\_o\_R5 <= rd0\_o\_R4; rd1\_o\_R2 <= rd1\_o\_R1 ; rd1\_o\_R3 <= rd1\_o\_R2; rd1\_o\_R4 <= rd1\_o\_R3; rd1\_o\_R5 <= rd1\_o\_R4; wr0\_o\_R2 <= wr0\_o\_R1; wr0\_o\_R3 <= wr0\_o\_R2; wr0\_o\_R4 <= wr0\_o\_R3; wr1\_o\_R2 <= wr1\_o\_R1; wr1\_o\_R3 <= wr1\_o\_R2; wr1\_o\_R4 <= wr1\_o\_R3; end always @(posedge clk\_in) begin if ( (rd0\_o\_R2 & ~rd1\_o\_R4) // pre-am rd if no ped on rnk 1 | rd0\_o\_R3 // 1st cyc of rd brst | rd0\_\_o\_\_R4 // 2nd cyc of rd brst | (rd0\_o\_R5 & ~rd1\_o\_R2 & ~rd1\_o\_R3) // post-rd cyc if no ped on rnk 1 (wr0 o R1) // pre-am wr wr0\_o\_R2 wr0\_o\_R3 // wr brst 1st & 2nd cyc (wr0 o R4) // post-wr cyc (chgef9) | wr1\_o\_R1 | wr1\_o\_R2 | wr1\_o\_R3 | wr1\_o\_R4 // rank 1 (chgef9) // enable fet en fet a  $\leq 1$  'b1; else // disable fet en fet a  $\leq 1$  'b0: end always @(posedge clk\_in) begin if ( (rd1\_o\_R2 & ~rd0\_o\_R4) | rd1\_o\_R3 |rd1\_o\_R4  $|(wr1_o_R1)|$ // (chgef8)  $\mid wr1\_o\_R2 \mid wr1\_o\_R3$  $|(wr1_o_R4)|$ // post-wr cyc (chgef9)  $| wr0\_o\_R1 | wr0\_o\_R2 | wr0\_o\_R3 | wr0\_o\_R4$ // rank 0 (chgef9) ) en\_fet\_b <= l 'b1; else en\_fet\_b <= 1 'b0; end

FIG. 2A schematically illustrates an exemplary memory module 10 which doubles the rank density in accordance 60 with certain embodiments described herein. The memory module 10 has a first memory capacity. The memory module 10 comprises a plurality of substantially identical memory devices 30 configured as a first rank 32 and a second rank 34. In certain embodiments, the memory devices 30 of the first 65 rank 32 are configured in pairs, and the memory devices 30 of the second rank 34 are also configured in pairs. In certain

embodiments, the memory devices **30** of the first rank **32** are configured with their respective DQS pins tied together and the memory devices **30** of the second rank **34** are configured with their respective DQS pins tied together, as described more fully below. The memory module **10** further comprises a logic element **40** which receives a first set of address and control signals from a memory controller (not shown) of the computer system. The first set of address and control signals is compatible with a second memory capacity substantially

equal to one-half of the first memory capacity. The logic element 40 translates the first set of address and control signals into a second set of address and control signals which is compatible with the first memory capacity of the memory module 10 and which is transmitted to the first rank 32 and 5 the second rank 34.

The first rank 32 of FIG. 2A has 18 memory devices 30 and the second rank 34 of FIG. 2A has 18 memory devices 30. Other numbers of memory devices 30 in each of the ranks 32, 34 are also compatible with embodiments 10 described herein.

In the embodiment schematically illustrated by FIG. 2A, the memory module 10 has a width of 8 bytes (or 64 bits) and each of the memory devices 30 of FIG. 2A has a bit width of 4 bits. The 4-bit-wide ("x4") memory devices 30 of 15 FIG. 2A have one-half the width, but twice the depth of 8-bit-wide ("x8") memory devices. Thus, each pair of "x4" memory devices 30 has the same density as a single "×8" memory device, and pairs of "x4" memory devices 30 can be used instead of individual "x8" memory devices to 20 provide the memory density of the memory module 10. For example, a pair of 512-Mb 128M×4-bit memory devices has the same memory density as a 1-Gb 128M×8-bit memory device.

For two "x4" memory devices 30 to work in tandem to 25 mimic a "x8" memory device, the relative DQS pins of the two memory devices 30 in certain embodiments are advantageously tied together, as described more fully below. In addition, to access the memory density of a high-density memory module 10 comprising pairs of "×4" memory 30 devices 30, an additional address line is used. While a high-density memory module comprising individual "×8" memory devices with the next-higher density would also utilize an additional address line, the additional address lines are different in the two memory module configurations.

For example, a 1-Gb 128M×8-bit DDR-1 DRAM memory device uses row addresses  $\mathrm{A}_{13}\text{-}\mathrm{A}_0$  and column addresses  $A_{11}$  and  $A_0$ - $A_0$ . A pair of 512-Mb 128M×4-bit DDR-1 DRAM memory devices uses row addresses A12-A0 and column addresses A12, A11, and A9-A0. In certain 40 embodiments, a memory controller of a computer system utilizing a 1-GB 128M×8 memory module 10 comprising pairs of the 512-Mb 128M×4 memory devices 30 supplies the address and control signals including the extra row address  $(A_{13})$  to the memory module 10. The logic element 45 40 receives the address and control signals from the memory controller and converts the extra row address  $(A_{13})$  into an extra column address (A12).

FIG. 2B schematically illustrates an exemplary logic element 40 compatible with embodiments described herein. 50 The logic element 40 is used for a memory module 10 comprising pairs of "×4" memory devices 30 which mimic individual "x8" memory devices. In certain embodiments, each pair has the respective DQS pins of the memory devices 30 tied together. In certain embodiments, as sche- 55 matically illustrated by FIG. 2B, the logic element 40 comprises a programmable-logic device (PLD) 42, a first multiplexer 44 electrically coupled to the first rank 32 of memory devices 30, and a second multiplexer 46 electrically coupled to the second rank 34 of memory devices 30. In 60 certain embodiments, the PLD 42 and the first and second multiplexers 44, 46 are discrete elements, while in, other certain embodiments, they are integrated within a single integrated circuit. Persons skilled in the art can select an appropriate PLD 42, first multiplexer 44, and second mul-65 tiplexer 46 in accordance with embodiments described herein.

In the exemplary logic element 40 of FIG. 2B, during a row access procedure (CAS is high), the first multiplexer 44 passes the  $A_{12}$  address through to the first rank 32, the second multiplexer 46 passes the  $A_{12}$  address through to the second rank 34, and the PLD 42 saves or latches the  $A_{13}$ address from the memory controller. In certain embodiments, a copy of the  $A_{13}$  address is saved by the PLD 42 for each of the internal banks (e.g., 4 internal banks) per memory device 30. During a subsequent column access procedure (CAS is low), the first multiplexer 44 passes the previously-saved  $A_{13}$  address through to the first rank 32 as the  $A_{12}$  address and the second multiplexer 46 passes the previously-saved A13 address through to the second rank 34 as the  $\mathrm{A}_{12}$  address. The first rank 32 and the second rank 34thus interpret the previously-saved A13 row address as the current  $A_{12}$  column address. In this way, in certain embodiments, the logic element 40 translates the extra row address into an extra column address in accordance with certain embodiments described herein.

Thus, by allowing two lower-density memory devices to be used rather than one higher-density memory device, certain embodiments described herein provide the advantage of using lower-cost, lower-density memory devices to build "next-generation" higher-density memory modules. Certain embodiments advantageously allow the use of lower-cost readily-available 512-Mb DDR-2 SDRAM devices to replace more expensive 1-Gb DDR-2 SDRAM devices. Certain embodiments advantageously reduce the total cost of the resultant memory module.

FIG. 3A schematically illustrates an exemplary memory module 10 which doubles number of ranks in accordance with certain embodiments described herein. The memory module 10 has a first plurality of memory locations with a first memory density. The memory module 10 comprises a plurality of substantially identical memory devices 30 configured as a first rank 32, a second rank 34, a third rank 36, and a fourth rank 38. The memory module 10 further comprises a logic element 40 which receives a first set of address and control signals from a memory controller (not shown). The first set of address and control signals is compatible with a second plurality of memory locations having a second memory density. The second memory density is substantially equal to one-half of the first memory density. The logic element 40 translates the first set of address and control signals into a second set of address and control signals which is compatible with the first plurality of memory locations of the memory module 10 and which is transmitted to the first rank 32, the second rank 34, the third rank 36, and the fourth rank 38.

Each rank 32, 34, 36, 38 of FIG. 3A has 9 memory devices 30. Other numbers of memory devices 30 in each of the ranks 32, 34, 36, 38 are also compatible with embodiments described herein.

In the embodiment schematically illustrated by FIG. 3A, the memory module 10 has a width of 8 bytes (or 64 bits) and each of the memory devices 30 of FIG. 3A has a bit width of 8 bits. Because the memory module 10 has twice the number of 8-bit-wide ("x8") memory devices 30 as does a standard 8-byte-wide memory module, the memory module 10 has twice the density as does a standard 8-byte-wide memory module. For example, a 1-GB 128M×8-byte memory module with 36 512-Mb 128M×8-bit memory devices (arranged in four ranks) has twice the memory density as a 512-Mb 128M×8-byte memory module with 18 512-Mb 128M×8-bit memory devices (arranged in two ranks).

To access the additional memory density of the highdensity memory module **10**, the two chip-select signals  $(CS_0, CS_1)$  are used with other address and control signals to gate a set of four gated CAS signals. For example, to access the additional ranks of four-rank 1-GB 128M×8-byte 5 DDR-1 DRAM memory module, the  $CS_0$  and  $CS_1$  signals along with the other address and control signals are used to gate the CAS signal appropriately, as schematically illustrated by FIG. **3**A. FIG. **3**B schematically illustrates an exemplary logic element **40** compatible with embodiments 10 described herein. In certain embodiments, the logic element **40** comprises a programmable-logic device (PLD) **42** and four "OR" logic elements **52**, **54**, **56**, **58** electrically coupled to corresponding ranks **32**, **34**, **36**, **38** of memory devices **30**.

In certain embodiments, the PLD **42** comprises an ASIC, 15 an FPGA, a custom-designed semiconductor device, or a CPLD. In certain embodiments, the PLD **42** and the four "OR" logic elements **52**, **54**, **56**, **58** are discrete elements, while in other certain embodiments, they are integrated within a single integrated circuit. Persons skilled in the art 20 can select an appropriate PLD **42** and appropriate "OR" logic elements **52**, **54**, **56**, **58** in accordance with embodiments described herein.

In the embodiment schematically illustrated by FIG. **3**B, the PLD **42** transmits each of the four "enabled CAS" <sup>25</sup> (ENCAS<sub>0</sub>a, ENCAS<sub>0</sub>b, ENCAS<sub>1</sub>a, ENCAS<sub>1</sub>b) signals to a corresponding one of the "OR" logic elements **52**, **54**, **56**, **58**. The CAS signal is also transmitted to each of the four "OR" logic elements **52**, **54**, **56**, **58**. The CAS signal and the "enabled CAS" signals are "low" true signals. By selectively <sup>30</sup> activating each of the four "enabled CAS" signals which are inputted into the four "OR" logic elements **52**, **54**, **56**, **58**, the PLD **42** is able to select which of the four ranks **32**, **34**, **36**, **38** is active.

In certain embodiments, the PLD **42** uses sequential and <sup>35</sup> combinatorial logic procedures to produce the gated CAS signals which are each transmitted to a corresponding one of the four ranks **32**, **34**, **36**, **38**. In certain other embodiments, the PLD **42** instead uses sequential and combinatorial logic procedures to produce four gated chip-select signals (e.g., <sup>40</sup>  $CS_0a$ ,  $CS_0b$ ,  $CS_1a$ , and  $CS_1b$ ) which are each transmitted to a corresponding one of the four ranks **32**, **34**, **36**, **38**.

#### Back-to-Back Adjacent Read Commands