## **EXHIBIT K**

## United States Patent [19]

[54] POWER SAVING FEATURE FOR

[11] Patent Number:

[45] Date of Patent: Dec. 27, 1994

|      | COMPONENTS HAVING BUILT-IN<br>TESTING LOGIC |                                                   |                 |

|------|---------------------------------------------|---------------------------------------------------|-----------------|

| [75] | Inventor:                                   | Michael D. Pedneau, Austin,                       | Tex.            |

| [73] | Assignee:                                   | Advanced Micro devices, Inc.<br>Sunnyvale, Calif. | •               |

| [21] | Appl. No.:                                  | 936,896                                           |                 |

| [22] | Filed:                                      | Aug. 27, 1992                                     |                 |

| [51] | Int. Cl.5                                   | H04B 17/00; G01F                                  | 31/02<br>6F 1/3 |

| [52] | U.S. Cl                                     | 371/22,5; 32                                      | 4/158.1         |

|      |                                             |                                                   |                 |

## 395/425; 395/750

[58] Field of Search 370/85.1, 94.1; 324/158 R, 158 SY

## References Cited

## U.S. PATENT DOCUMENTS

| 4,969,146 | 11/1990 | Twitty et al        | 370/85.1 |

|-----------|---------|---------------------|----------|

|           |         | Markkula, Jr. et al |          |

| 5,034,882 | 7/1991  | Eisenhard et al     | 395/650  |

| 5,060,138 | 10/1991 | Gephardt et al      | 395/275  |

|           |         | Huribut et al       |          |

| 5.212.442 | 5/1993  | O'Toole et al.      | 371/21.1 |

| 5,212,694 | 5/1993  | Fujiwara 371/21.1    |  |

|-----------|---------|----------------------|--|

| 5,222,066 | 6/1993  | Grula et al 371/21.1 |  |

| 5,224,101 | 6/1993  | Popyack, Jr 371/15.1 |  |

| 5,241,680 | 8/1993  | Cole et al 395/750   |  |

| 5,274,778 | 12/1993 | Hall 371/21.1        |  |

Primary Examiner-Emanuel T. Voeltz Assistant Examiner-Alan Tran Attorney, Agent, or Firm-Foley & Lardner

## ABSTRACT

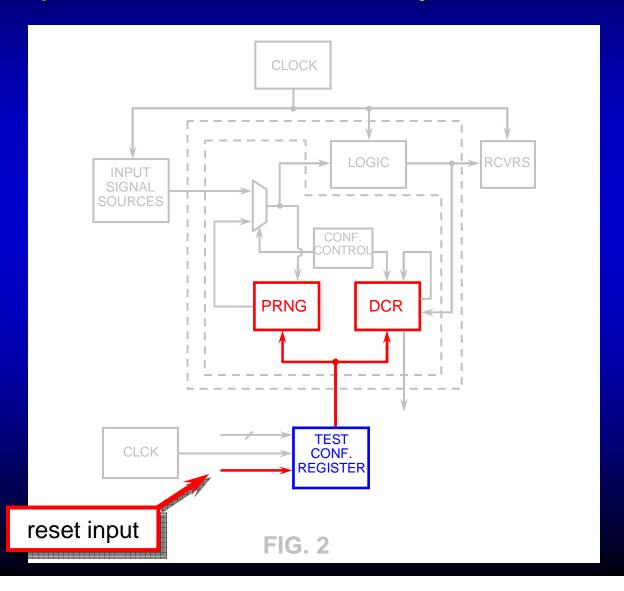

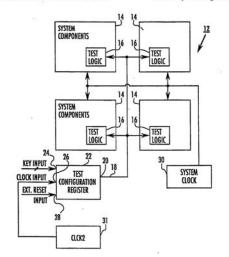

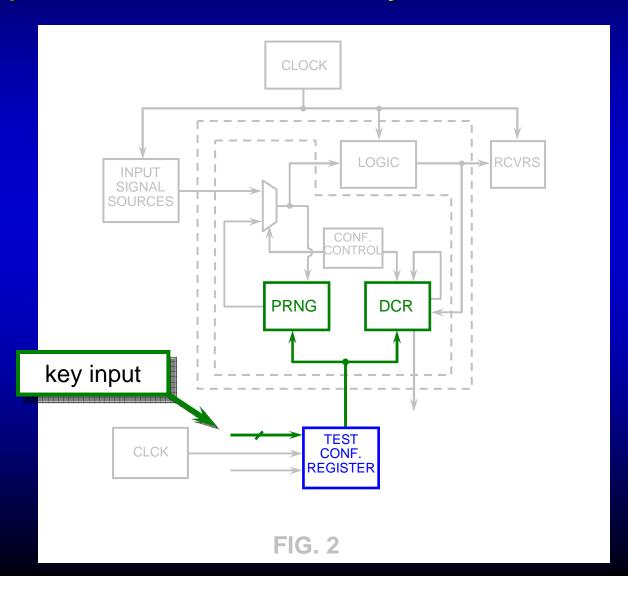

A configuration register enables built-in testing logic during testing operations, and disables the testing logic during non-testing operations. When enabled, the testing logic is in a normal state, and when disabled the testing logic is in a low power state. The configuration register generates a control signal to the testing logic, register generates a control signal to the testing logic, the control signal being is responsive to signals received at a key input and a reset input of the configuration register. When the reset input of the configuration regis-ter is triggered, the control signal drives the testing logic to the low power state. When a signal matching a predetermined data pattern is applied to the key input, the control signal drives the testing logic to the normal

## 24 Claims, 3 Drawing Sheets

## **Pedneau U.S. Patent No.**

5,377,200

# Pedneau: '200 Patent Technology

# Power-saving feature for processors having testing logic.

- Testing logic is used during product design to work out bugs and streamline the manufacturing process.

- Testing logic is used during the manufacturing process to improve yield (percent of products with no defects).

- Testing logic consumes power.

## Pedneau: '200 Patent The Problem the Invention Addresses

In the prior art, the testing logic was always powered even though it was used only a miniscule percentage of the time. This was a waste of power.

## Pedneau: '200 Patent Statement of the Invention

The invention is a system for controlling the power consumed by testing logic so that it consumes minimal power when not being utilized.

## Pedneau: '200 Patent Pedneau's Invention

**Key Input Activated – Test Circuitry in Normal Power State**

## Pedneau: '200 Patent Pedneau's Invention

Reset Input Activated - Test Circuitry in Low Power State