### **EXHIBIT F**

### US00555990A

#### United States Patent [19]

Cheng et al.

[11] Patent Number:

[45] Date of Patent:

#### [54] MEMORIES WITH BURST MODE ACCESS

[75] Inventors: Pearl P. Cheng, Cupertino; Michael S. Briner; James C. Yu, both of San Jose,

[73] Assignce: Advanced Micro Devices, Inc., Sunnyvale, Calif.

[21] Appl. No.: 328,337

[22] Filed: Oct. 24, 1994

#### Related U.S. Application Data

| [63] | Continuation of Ser. No. 836,667, Feb. 14, 1992, abandoned. |

|------|-------------------------------------------------------------|

| [51] | Int. Cl.6                                                   |

| [52] | U.S. Cl                                                     |

| [58] | Field of Search                                             |

#### References Cited

#### U.S. PATENT DOCUMENTS

| 4,347,587 |         | Rao 365/189              |

|-----------|---------|--------------------------|

| 4,513,372 | 4/1985  | Ziegler et al 365/230.03 |

| 4,621,320 | 11/1986 | Holste et al             |

| 4,636,986 | 1/1987  | Pinkham 365/195          |

|           |         | Tam                      |

| 4,805,094 | 2/1989  | Oye et al 395/25         |

| 4,811,297 | 3/1989  | Ogawa 365/189.02         |

| 4,833,657 | 5/1989  | Tanaka                   |

| 4,849,937 | 7/1989  | Yoshimoto 365/189.05     |

| 4,872,143 | 10/1989 | Sumi                     |

| 4,954,987 | 9/1990  | Auvinen et al            |

| 5,051,889 |         | Fung et al               |

### 5,146,582 9/1992 Begun 395/500 5,241,510 8/1993 Kobayashi et al. 365/230.03 5,280,594 1/1994 Young et al. 395/425

#### OTHER PUBLICATIONS

Choosing Memory Architectures to Balance Cost and Performance, Microprocessor Reports, vol. 2, No. 9, pp. 6-9,

(Sep. 1988). C. A. Holt, Electronic Circuits (John Wiley & Sons, 1978),

John F. Wakerly, Digital Design: Principles and Practices (Prentice-Hall, 1990), pp. 123, 126-127, 246-254 and

Primary Examiner-Rebecca L. Rudolph

Attorney, Agent, or Firm—Skjerven, Morrill, MacPherson, Franklin & Friel; Michael Shenker

#### ABSTRACT

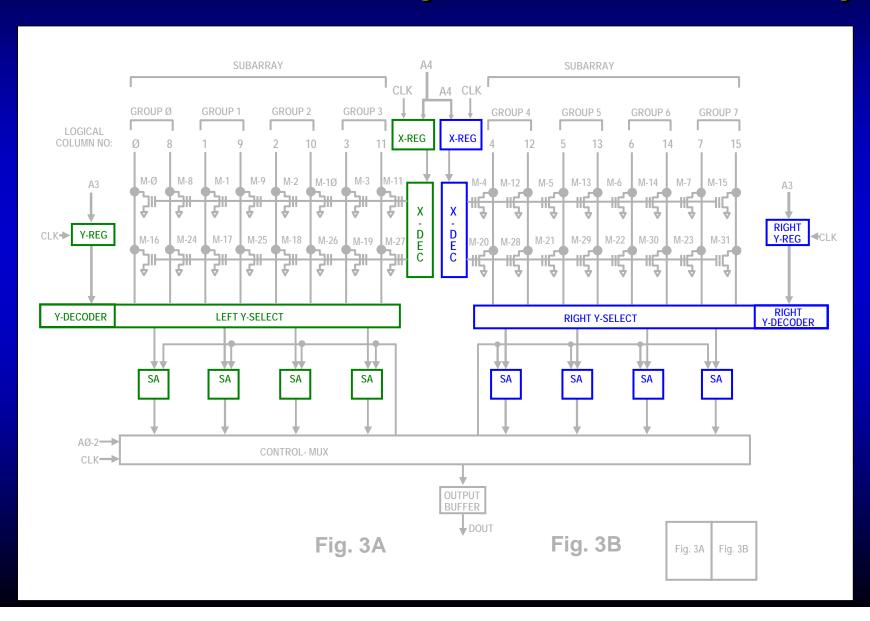

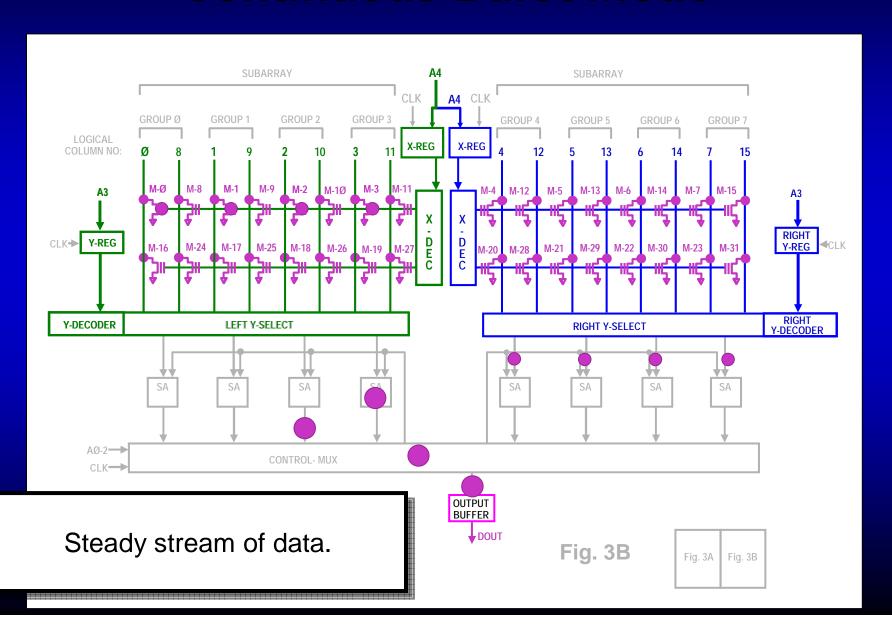

To provide a boundaryless burst mode access, a memory array is divided into two or more subarrays. Each subarray has its own row and column decoders. The columns of each subarray are divided into groups. A sense amplifier circuit is provided for each group of columns. The column decoder of each subarray selects simultaneously one column from each group so that the memory locations in one row in the selected columns have consecutive addresses. The memory locations in the selected row and columns are read by the sense amplifier circuits. While the contents of the sense amplifier circuits of one subarray are transferred one by one to the memory output, consecutive memory locations of another subarray are read to the sense amplifier circuits. In some embodiments, to save power, sense amplifier circuits are disabled when their outputs are not transferred to the memory output.

#### 23 Claims, 37 Drawing Sheets

## Cheng U.S. Patent No. 5,559,990

## Cheng: '990 Patent Statement of the Invention

The invention is a memory with dedicated circuitry for each of its subarrays that maximizes the performance of memory by providing for continuous burst mode reads and selective deactivation of sense amplifiers.

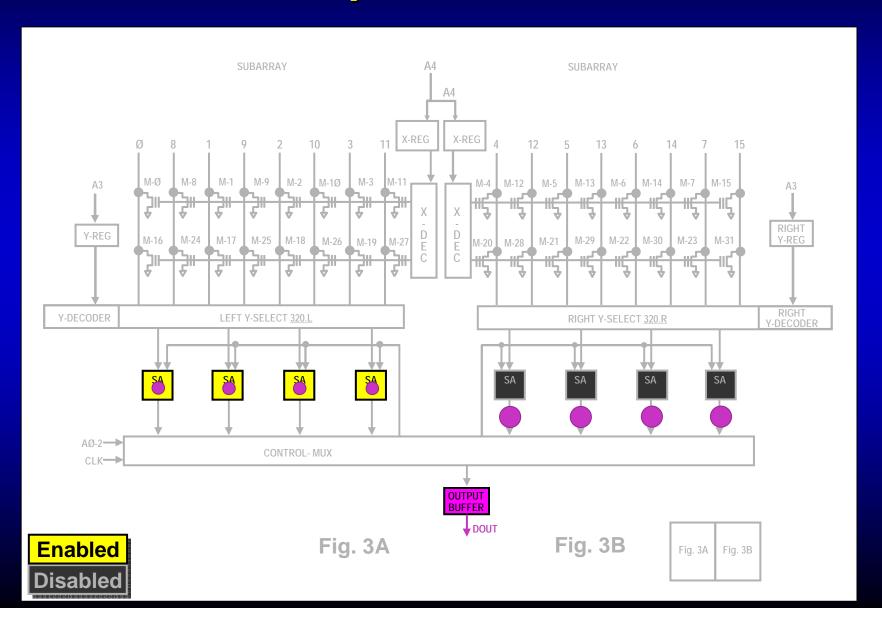

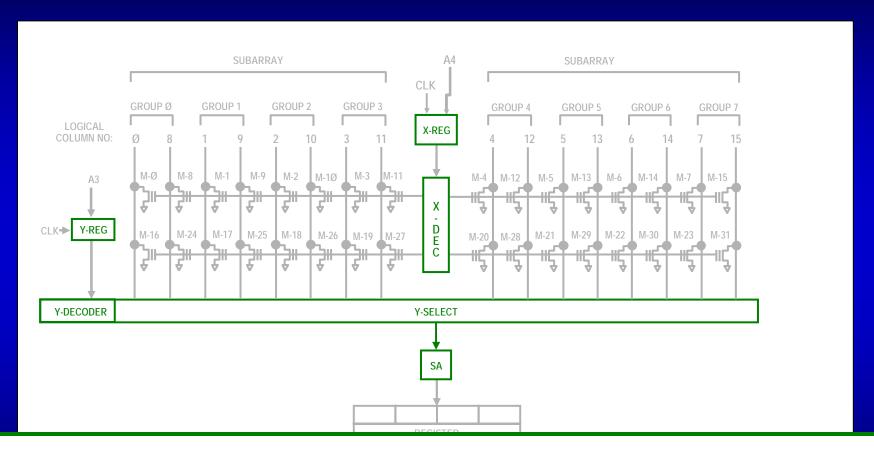

# Cheng: '990 Patent Prior Art: Shared Circuitry for Subarrays

Only one X-register, X- decoder, Y-register, Y-decoder and sense amplifier for both subarrays.

# Cheng: '990 Patent Dedicated Circuitry for Each Subarray

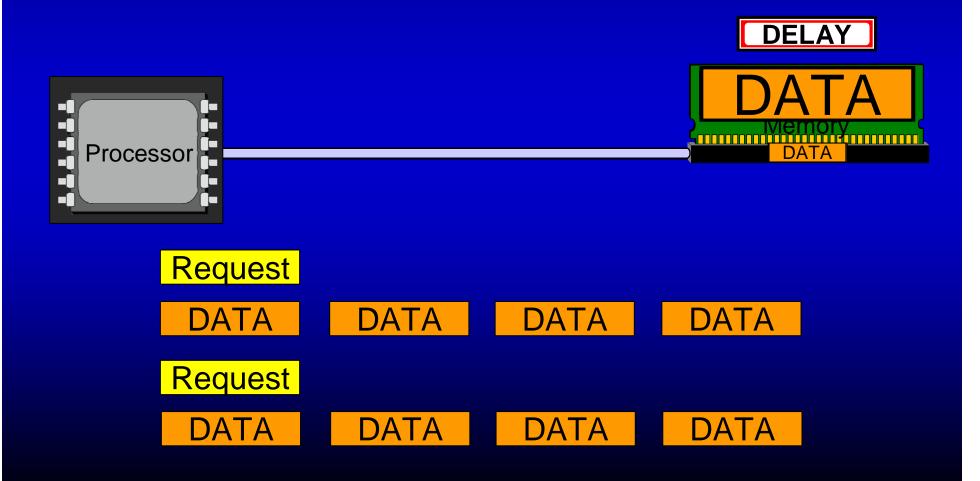

### **Memory Access: Burst Mode Access**

### **Continuous Burst Mode**

Request

DATA

DATA

**DATA**

**DATA**

DATA

DATA

DATA

DATA

**DATA**

DATA

DATA

DATA

## Cheng: '990 Patent Continuous Burst Mode

# Cheng: '990 Patent Sense Amplifier Deactivation