### **EXHIBIT H**

### United States Patent [19]

Patel et al.

[54] INTEGRATED CIRCUIT STRUCTURE HAVING COMPENSATING MEANS FOR SELF-INDUCTANCE EFFECTS

[75] Inventors: Bharat D. Patel, San Jose; Stephen Y. Tam, San Francisco; Pravin R. Shah, Sunnyvale, all of Calif.

[73] Assignee: Advanced Micro Devices, Inc., Sunnyvale, Calif.

[21] Appl. No.: 817,227

21 Filed: Jan 8 19

| [51] | Int. Cl.4 |                                |

|------|-----------|--------------------------------|

| [52] | U.S. Cl.  |                                |

|      |           | 357/45: 357/46: 357/51: 357/68 |

[11] Patent Number:

4,737,830

[45] Date of Patent: Apr. 12, 1988

### References Cited

### U.S. PATENT DOCUMENTS

| 4,493,056 | 1/1985 | Mao        | 357/23.6 |

|-----------|--------|------------|----------|

| 4,516,312 | 5/1985 | Tomita     | 357/23.6 |

| 4.536.941 | 8/1985 | Kun et al. | 357/23.6 |

Primary Examiner—Edward J. Wojciechowicz Attorney, Agent, or Firm—Patrick T. King; John P. Taylor; J. Vincent Tortolano

### [57] ABSTRACT

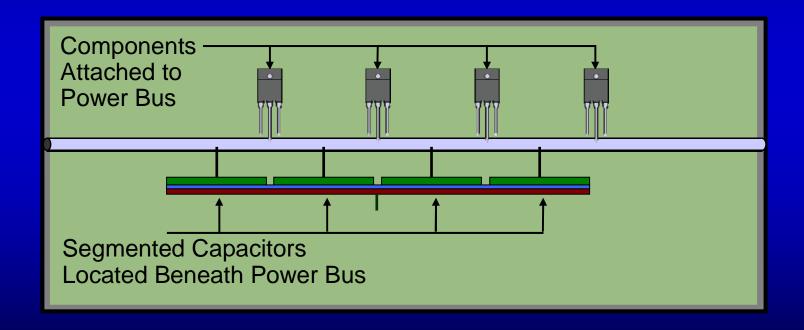

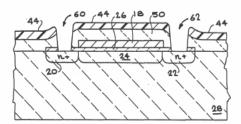

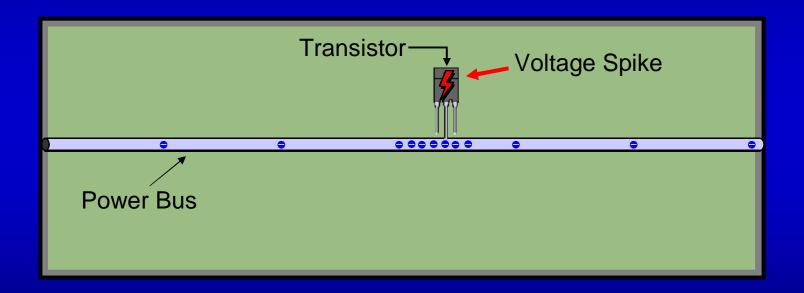

An improved integrated circuit structure is disclosed which comprises a Vcc bus and a Vss bus having capacitance means coupled between the busses and distributed along the length of the busses to reduce the voltage spikes induced during switching. In a preferred embodiment, the capacitance means comprise one or more capacitors formed beneath one of the busses. Construction of MOS capacitors beneath one or more of the busses is disclosed.

6 Claims, 11 Drawing Sheets

# Patel U.S. Patent No. 4,737,830

## Voltage Spikes Damaged Transistors Attached to Power Bus

### Patel: '830 Patent Statement of the Invention

Adding capacitance underneath the busses to reduce voltage spikes. The gate area of the capacitor is segmented, with each segment having a connection to the bus to improve efficiency and reliability.

## Patel: '830 Patent Invention