# Exhibit 3

Dockets.Justia.com

U 7485348

# HOP UNITED STAVERS O BANDERI

# TO ALL TO WHOM THESE PRESENTS SHALL COME:

UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office

July 07, 2014

THIS IS TO CERTIFY THAT ANNEXED HERETO IS A TRUE COPY FROM THE RECORDS OF THIS OFFICE OF:

U.S. PATENT: *8,073,150* ISSUE DATE: *December 06, 2011*

> By Authority of the Under Secretary of Commerce for Intellectual Property and Director of the United States Patent and Trademark Office

111. 1 an

M. TARVER Certifying Officer

# (12) United States Patent

# Joho et al.

# (54) DYNAMICALLY CONFIGURABLE ANR SIGNAL PROCESSING TOPOLOGY

- (75) Inventors: Marcel Joho, Framingham, MA (US); Ricardo F. Carreras, Southborough, MA (US)

- Assignee: Bose Corporation, Framingham, MA (73)(US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 420 days.

- (21) Appl. No.: 12/430,990

- Filed: Apr. 28, 2009 (22)

### (65) **Prior Publication Data**

US 2010/0272277 A1 Oct. 28, 2010

- (51) Int. Cl.

- G10K 11/16 (2006.01)

- (52) Field of Classification Search ...... 381/71.6 (58)

- See application file for complete search history.

### (56) **References** Cited

# U.S. PATENT DOCUMENTS

| 4,455,675 | Δ |   | 6/1084  | Bose et al.             |

|-----------|---|---|---------|-------------------------|

|           |   |   |         |                         |

| 5,018,202 | А |   | 5/1991  | Takahashi et al.        |

| 5,138,664 | Α |   | 8/1992  | Kimura et al.           |

| 5,172,416 | Α |   | 12/1992 | Allie et al.            |

| 5,202,927 | Α |   | 4/1993  | Topholm                 |

| 5,255,325 | Α |   | 10/1993 | Ishimitsu et al.        |

| 5,303,306 | Α | * | 4/1994  | Brillhart et al 381/315 |

| 5,337,366 | Α | * | 8/1994  | Eguchi et al 381/71.11  |

| 5,388,062 | Α | * | 2/1995  | Knutson 708/323         |

| 5,416,846 | Α |   | 5/1995  | Tamura et al.           |

| 5,452,361 | Α |   | 9/1995  | Jones                   |

| 5,481,615 | Α |   | 1/1996  | Eatwell et al.          |

| 5,699,436 | Α |   | 12/1997 | Claybaugh et al.        |

| 5,710,819 | Α | * | 1/1998  | T.o slashed.pholm       |

|           |   |   |         | et al                   |

### US 8,073,150 B2 (10) Patent No.:

### Dec. 6, 2011 (45) Date of Patent:

| 5,724,433 A |   | 3/1998  | Engebretson et al.        |  |  |

|-------------|---|---------|---------------------------|--|--|

| 5,815,582 A |   | 9/1998  | Claybaugh et al.          |  |  |

| 5,825,897 A |   | 10/1998 | Andrea et al.             |  |  |

| 5,841,856 A |   | 11/1998 | Ide                       |  |  |

| 6,035,050 A | * | 3/2000  | Weinfurtner et al 381/313 |  |  |

| 6,041,126 A |   | 3/2000  | Terai et al.              |  |  |

| 6,061,456 A |   | 5/2000  | Andrea et al.             |  |  |

| 6,094,489 A |   | 7/2000  | Ishige et al.             |  |  |

| 6,118,878 A |   | 9/2000  | Jones                     |  |  |

| 6,160,893 A | * | 12/2000 | Saunders et al 381/71.6   |  |  |

| (Continued) |   |         |                           |  |  |

FOREIGN PATENT DOCUMENTS

3733132 A1 4/1989 (Continued)

# OTHER PUBLICATIONS

Invitation to Pay Additional Fees dated Jul. 26, 2010 for PCT/2010/ 032486.

# (Continued)

Primary Examiner - Elvin G Enad Assistant Examiner - Robert W Horn

DE

### ABSTRACT (57)

In an ANR circuit, possibly of a personal ANR device, each of a feedback ANR pathway in which feedback anti-noise sounds are generated from feedback reference sounds, a feedforward ANR pathway in which feedforward anti-noise sounds are generated from feedforward reference sounds, and a pass-through audio pathway in which modified passthrough audio sounds are generated from received passthrough audio sounds incorporate at least a block of filters to perform those functions; and may each incorporate one or more VGAs and/or summing nodes. For each of these pathways, ANR settings for interconnections of each of the pathways, coefficients of each of the filters, gain settings of any VGA, along with still other ANR settings, are dynamically configurable wherein dynamic configuration is performed in synchronization with the transfer of one or more pieces of digital data along one or more of the pathways.

# 24 Claims, 18 Drawing Sheets

# Page 2

# U.S. PATENT DOCUMENTS

| 6,236,731 B1                       | <sup>▶</sup> 5/2001 | Brennan et al 381/316    |

|------------------------------------|---------------------|--------------------------|

| 6,418,228 B1                       | 7/2002              | Terai et al.             |

| 6,522,753 B1                       | * 2/2003            | Matsuzawa et al 381/71.1 |

| 6,567,524 B1                       | 5/2003              |                          |

| 6,717,537 B1                       | 4/2004              |                          |

| 6,741,707 B2                       | 5/2004              | Ray et al.               |

| 6,744,882 B1                       | 6/2004              | Gupta et al.             |

| 6,829,365 B1                       | 12/2004             | Kim                      |

| 6,870,940 B2 '                     | * 3/2005            | Meyer et al 381/314      |

| 6,937,738 B2                       | 8/2005              | Armstrong et al.         |

| 6,993,140 B1                       | 1/2006              | Chen                     |

| 6,996,241 B2                       | 2/2006              | Ray et al.               |

| 7,039,195 B1                       | 5/2006              | Svean et al.             |

| 7,215,766 B2                       | 5/2007              | Wurtz                    |

| 7,216,139 B2                       | \$ 5/2007           | Langhammer et al 708/501 |

| 7,248,705 B1                       | 7/2007              | Mishan                   |

| 7,251,335 B1                       | 7/2007              | Chen                     |

| 7,260,209 B2                       | 8/2007              | Harvey et al.            |

| 7,277,722 B2                       | 10/2007             | Rosenzweig               |

| 7,292,973 B1                       | 11/2007             | Johnston et al 704/200.1 |

| 7,317,802 B2                       | 1/2008              | Wurtz                    |

| 7,433,481 B2                       | 10/2008             | Armstrong et al.         |

| 7,627,127 B2                       | 12/2009             | Aida et al.              |

| 7,706,550 B2                       | 4/2010              | Amada et al.             |

| 7,813,515 B2                       |                     | Botti et al 381/120      |

| 7,822,210 B2                       |                     | Barnhill 381/2           |

| 7,853,028 B2                       |                     | Fischer                  |

| 7,885,422 B2                       |                     | Sinai                    |

| 7,933,420 B2                       |                     | Copley et al 381/71.11   |

| 7,945,065 B2*                      |                     | Menzl et al 381/314      |

| 7,983,908 B2*                      |                     | Kuboki et al 704/228     |

| 2001/0039190 A1                    | 11/2001             | Bhatnagar                |

| 2003/0021429 A1*                   |                     | Ratcliff et al           |

| 2003/0053636 A1*                   |                     | Goldberg et al           |

| 2003/0228019 A1                    | 12/2003             | Eichler et al.           |

| 2004/0138769 A1                    | 7/2004              | Akiho                    |

| 2004/0240677 A1                    | 12/2004             | Onishi et al.            |

| 2005/0025323 A1*                   |                     | Botti et al              |

| 2005/0069146 A1                    | 3/2005              | Bum                      |

| 2005/0078845 A1*                   |                     | Aschoff et al            |

| 2005/0117754 A1                    | 6/2005              | Sakawaki                 |

| 2006/0088171 A1                    | 4/2006              | Yeh                      |

| 2007/0003078 A1                    | 1/2007              | Escott et al.            |

| 2007/0076896 A1                    | 4/2007              | Hosaka et al.            |

| 2007/0223715 A1                    | 9/2007              | Barath et al.            |

| 2007/02250314 A1                   | 10/2007             | Kuboki et al.            |

| 2007/0253569 A1                    | 11/2007             | Bose                     |

| 2007/0255509 A1                    | 1/2007              | Romesburg                |

| 2008/0025550 A1<br>2008/0037801 A1 | 2/2008              | Alves et al.             |

| 2000/000/001 /M                    | 22000               | ·                        |

|                                    |                     |                          |

| 2000/0005202 |       | 1/2000  | D ( 1                      |

|--------------|-------|---------|----------------------------|

| 2008/0095383 |       | 4/2008  | Pan et al.                 |

| 2008/0162072 |       | 7/2008  | Copley et al.              |

| 2008/0165981 |       | 7/2008  | Wurtz                      |

| 2008/0192957 | • • • | 8/2008  | Kubo                       |

| 2008/0207123 |       | 8/2008  | Andersen 455/41.1          |

| 2008/0292113 |       | 11/2008 | Tian                       |

| 2008/0310652 |       | 12/2008 | Gustavsson                 |

| 2009/0034748 |       | 2/2009  | Sibbald                    |

| 2009/0034768 |       | 2/2009  | Lunner 381/318             |

| 2009/0103750 | A1*   | 4/2009  | Chilakapati et al 381/94.5 |

| 2009/0161889 | A1    | 6/2009  | Magrath                    |

| 2010/0166203 | A1    | 7/2010  | Peissig et al.             |

| 2010/0254550 | A1*   | 10/2010 | Martin et al 381/123       |

| 2010/0260362 | A1*   | 10/2010 | Sander et al 381/309       |

| 2010/0266136 | A1    | 10/2010 | Kelloniemi et al.          |

| 2010/0266137 | A1*   | 10/2010 | Sibbald et al              |

| 2010/0272275 | A1*   | 10/2010 | Carreras et al 381/71.6    |

| 2010/0272276 | A1*   | 10/2010 | Carreras et al 381/71.6    |

| 2010/0272277 | Al    | 10/2010 | Joho et al.                |

| 2010/0272278 | A1*   | 10/2010 | Joho et al                 |

| 2010/0272279 | A1*   | 10/2010 | Joho et al 381/71.6        |

| 2010/0272280 | A1*   | 10/2010 | Joho et al                 |

| 2010/0272281 | A1*   | 10/2010 | Carreras et al             |

| 2010/0272282 | A1*   | 10/2010 | Carreras                   |

| 2010/0272283 | A1    | 10/2010 | Carreras                   |

| 2010/0272284 | A1*   | 10/2010 | Joho et al                 |

| 2010/0274564 | A1*   | 10/2010 | Bakalos et al 704/500      |

| 2010/0310086 | A1*   | 12/2010 | Magrath et al              |

| 2010/0322432 | A1*   | 12/2010 | Clemow                     |

| 2011/0130176 |       | 6/2011  | Magrath et al 455/570      |

| 2011/0188665 | AI    | 8/2011  | Burge                      |

|              |       |         |                            |

# FOREIGN PATENT DOCUMENTS

| JP | 2254898 A     | 10/1990 |

|----|---------------|---------|

| ЛЪ | 5341792 A     | 12/1993 |

| ЪЪ | 8006571 A     | 1/1996  |

| JP | 2005257720 A  | 9/2005  |

| WO | 2005112849 A2 | 12/2005 |

| WO | 2009041012 A1 | 4/2009  |

# OTHER PUBLICATIONS

International Search Report and Written Opinion dated Oct. 1, 2010

for PCT/2010/032486. Invitation to Pay Additional Fees dated Aug. 3, 2010 for PCT/ US2010/032557. International Search Report and Written Opinion dated Sep. 16, 2010 for PCT/US10/032557.

\* cited by examiner

:

FIG. 2a

FIG. 2b

Copy provided by USPTO from the PIRS Image Database on 07/01/2014

FIG. 2e

FIG. 4b

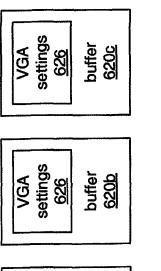

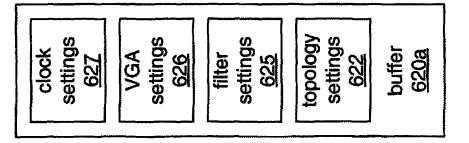

VGA settings <u>626</u> buffer <u>620a</u>

FIG. 6a

FIG. 6c

# DYNAMICALLY CONFIGURABLE ANR SIGNAL PROCESSING TOPOLOGY

# TECHNICAL FIELD

This disclosure relates to personal active noise reduction (ANR) devices to reduce acoustic noise in the vicinity of at least one of a user's ears.

# BACKGROUND

Headphones and other physical configurations of personal ANR device worn about the ears of a user for purposes of isolating the user's ears from unwanted environmental sounds have become commonplace. In particular, ANR head- 15 phones in which unwanted environmental noise sounds are countered with the active generation of anti-noise sounds, have become highly prevalent, even in comparison to headphones or ear plugs employing only passive noise reduction (PNR) technology, in which a user's ears are simply physi-20 cally isolated from environmental noises. Especially of interest to users are ANR headphones that also incorporate audio listening functionality, thereby enabling a user to listen to electronically provided audio (e.g., playback of recorded audio or audio received from another device) without the 25 intrusion of unwanted environmental noise sounds.

Unfortunately, despite various improvements made over time, existing personal ANR devices continue to suffer from a variety of drawbacks. Foremost among those drawbacks are undesirably high rates of power consumption leading to short <sup>30</sup> battery life, undesirably narrow ranges of audible frequencies in which unwanted environmental noise sounds are countered through ANR, instances of unpleasant ANR-originated sounds, and instances of actually creating more unwanted noise sounds than whatever unwanted environmental sounds <sup>35</sup> may be reduced.

## SUMMARY

In an ANR circuit, possibly of a personal ANR device, each 40 of a feedback ANR pathway in which feedback anti-noise sounds are generated from feedback reference sounds, a feedforward ANR pathway in which feedforward anti-noise sounds are generated from feedforward reference sounds, and a pass-through audio pathway in which modified pass- 45 through audio sounds are generated from received passthrough audio sounds incorporate at least a block of filters to perform those functions; and may each incorporate one or more VGAs and/or summing nodes. For each of these pathways, ANR settings for interconnections of each of the path- 50 ways, coefficients of each of the filters, gain settings of any VGA, along with still other ANR settings, are dynamically configurable wherein dynamic configuration is performed in synchronization with the transfer of one or more pieces of digital data along one or more of the pathways.

In one aspect, a method of operating a dynamically configurable ANR circuit to provide ANR in an earpiece of a personal ANR device includes: incorporating a first ADC of the ANR circuit, a first plurality of digital filters of a quantity specified by a first set of ANR settings, and a DAC of the ANR 60 circuit into a first pathway; incorporating a second ADC of the ANR circuit, a second plurality of digital filters of a quantity specified by the first set of ANR settings, and the DAC into a second pathway; selecting a type of digital filter specified by the first set of ANR settings for each digital filter of the first 65 and second pluralities of digital filters from among a plurality of types of digital filter supported by the ANR circuit; adopt-

ing a signal processing topology specified by the first set of ANR settings by configuring interconnections among at least the first and second ADCs, the first and second pluralities of digital filters and the DAC so that digital data representing sounds flows through the first pathway from the first ADC to the DAC through at least the first plurality of digital filters; digital data representing sounds flows through the second pathway from the second ADC to the DAC through at least the second plurality of digital filters; and the first and second 10 pathways are combined at a first location along the first pathway and at a second location along the second pathway such that the digital data from both the first and second pathways are combined before flowing to the DAC; configuring each digital filter of the first and second pluralities of digital filters with filter coefficients specified by the first set of ANR settings; setting a data transfer rate at which digital data flows through at least a portion of at least one of the first and second pathways as specified by the first ANR settings; operating the first and second ADCs, the first and second pluralities of digital filters and the DAC to provide ANR in the earpiece; and changing an ANR setting specified by the first set of ANR settings to an ANR setting specified by a second set of ANR settings in synchronization with a transfer of digital data along at least a portion of at least one of the first and second pathways.

Implementations may include, and are not limited to, one or more of the following features. The method may further include incorporating a third ADC of the ANR circuit, a third plurality of digital filters of a quantity specified by a first set of ANR settings, and the DAC into a third pathway; selecting a type of digital filter specified by the first set of ANR settings for each digital filter of the third plurality of digital filters from among the plurality of types of digital filter supported by the ANR circuit; adopting a signal processing topology specified by the first set of ANR settings further comprises configuring interconnections among a third ADC, the third plurality of digital filters and the DAC so that digital data representing sounds flows through the third pathway from the third ADC to the DAC through at least the third plurality of digital filters, and the third pathway is combined with one of the first and second pathways at a third location along the third pathway and at a fourth location along the one of the first and second pathways such that the digital data from the third pathway and the one of the first and second pathways are combined before flowing to the DAC; configuring each digital filter of the third plurality of digital filters with filter coefficients specified by the first set of ANR settings; and operating the third ADC and the third plurality of digital filters, in conjunction with operating the first and second ADCs, the first and second pluralities of digital filters and the DAC to provide ANR in the earpiece.

The method may further include monitoring an amount of power available from a power source, wherein changing an ANR setting specified by the first set of ANR settings to an ANR setting specified by the second set of ANR settings 55 occurs in response to a reduction in the amount of power available from the power source; or monitoring a characteristic of a sound represented by digital data, wherein changing an ANR setting specified by the first set of ANR settings to an ANR setting specified by the second set of ANR settings occurs in response to a change in the characteristic; and either way, wherein changing the ANR setting specified by the first set of ANR settings to an ANR setting specified by the second set of ANR settings includes changing at least one of an interconnection of the signal processing topology defined by the first ANR settings, a selection of a digital filter specified by the first ANR settings, a filter coefficient specified by the

first ANR settings, and a data transfer rate specified by the first ANR settings. The method may further include awaiting receipt of the second set of ANR settings from an external processing device coupled to the ANR circuit; wherein changing an ANR setting specified by the first set of ANR settings to an ANR setting specified by the second set of ANR settings occurs in response to receiving the second set of ANR settings from the external processing device. It may be that in the method: the first set of ANR settings specifies a third location along the first pathway and a fourth location along 10 the second pathway at which the first and second pathways are combined; the first set of ANR settings specifies a split in the second pathway that creates a first branch in the second pathway that is combined with the first pathway at the first location along the first pathway and the second location along 15 second pathway, and creates a second branch in the second pathway that is combined with the first pathway at the third location along the first pathway and the fourth location along the second pathway; and adopting a signal processing topology specified by the first set of ANR settings further com- 20 prises configuring interconnections among the first and second ADCs, the first and second pluralities of filters and the DAC to create the first and second branches of the second pathway.

In one aspect, an apparatus includes an ANR circuit, and 25 the ANR circuit includes a first ADC; a second ADC; a DAC; a processing device; and a storage in which is stored a sequence of instructions. When the sequence of instructions is executed by the processing device, the processing device is caused to: incorporate the first ADC, a first plurality of digital 30 filters of a quantity specified by a first set of ANR settings, and the DAC into a first pathway; incorporate the second ADC, a second plurality of digital filters of a quantity specified by the first set of ANR settings, and the DAC into a second pathway; select a type of digital filter specified by the first set of ANR 35 settings for each digital filter of the first and second pluralities of digital filters from among a plurality of types of digital filter supported by the ANR circuit; adopt a signal processing topology specified by the first set of ANR settings by configuring interconnections among at least the first and second ADCs, the first and second pluralities of digital filters and the DAC so that digital data representing sounds flows through the first pathway from the first ADC to the DAC through at least the first plurality of digital filters; digital data representing sounds flows through the second pathway from the second 45 ADC to the DAC through at least the second plurality of digital filters; and the first and second pathways are combined at a first location along the first pathway and at a second location along the second pathway such that the digital data from both the first and second pathways are combined before 50 flowing to the DAC; configure each digital filter of the first and second pluralities of digital filters with filter coefficients specified by the first set of ANR settings; set a data transfer rate at which digital data flows through at least a portion of at first ANR settings; cause the first and second ADCs, the first and second pluralities of digital filters and the DAC to be operated to provide ANR in the earpiece; and change an ANR setting specified by the first set of ANR settings to an ANR setting specified by a second set of ANR settings in synchro- 60 nization with a transfer of digital data along at least a portion of at least one of the first and second pathways.

Implementations may include, and are not limited to, one or more of the following features. In the ANR circuit, it may be that a plurality of filter routines that defines a plurality of 65 types of digital filter is stored in the storage; each filter routine of the plurality of filter routines comprises a sequence of

instructions that when executed by the processing device causes the processing device to perform filter calculations of the type of digital filter; and the processing device is further caused to instantiate each digital filter of the first and second pluralities of digital filters based on filter routines of the plurality of filter routines that defines the type of digital filter specified by the first set of ANR settings. The processing device may directly transfer digital data among the first and second ADCs, each of the digital filters of the first and second pluralities of digital filters instantiated by the processing device, and the DAC, and/or the processing device may operate a DMA device to transfer digital data among at least a subset of the first and second ADCs, each of the digital filters of the first and second pluralities of digital filters instantiated by the processing device, and the DAC.

The ANR circuit may further include an interface to enable an amount of power available from a power source coupled to the ANR circuit to be monitored, and the processing device may be further caused to: monitor the amount of power available from the power source; and change an ANR setting specified by the first set of ANR settings to an ANR setting specified by the second set of ANR settings in response to a reduction in the amount of power available from the power source, wherein the change comprises a change of at least one of an interconnection of the signal processing topology defined by the first ANR settings, a selection of a digital filter specified by the first ANR settings, a filter coefficient specified by the first ANR settings, and a data transfer rate specified by the first ANR settings. The processing device may be further caused to monitor a characteristic of a sound represented by digital data; and change an ANR setting specified by the first set of ANR settings to an ANR setting specified by the second set of ANR settings in response to a change in the characteristic, wherein the change comprises a change of at least one of an interconnection of the signal processing topology defined by the first ANR settings, a selection of a digital filter specified by the first ANR settings, a filter coefficient specified by the first ANR settings, and a data transfer rate specified by the first ANR settings. The processing device may be further caused to configure interconnections among the first ADC, the first plurality of digital filters, the DAC and a VGA; and configure the VGA with a gain setting specified by the first set of ANR settings; cause the VGA to be operated in conjunction with the first and second ADCs, the first and second pluralities of digital filters and the DAC to provide ANR in the earpiece; wherein the processing device being caused to change an ANR setting specified by the first set of ANR settings to an ANR setting specified by the second set of ANR settings comprises the processing device being caused to configure the VGA with a gain setting specified by the second set of ANR settings. The apparatus may further include an external processing device external to the ANR circuit: wherein the ANR circuit further comprises an interface coupling the ANR circuit to the external processing least one of the first and second pathways as specified by the 55 device; and wherein the processing device of the ANR circuit is further caused to await receipt of the second set of ANR settings from the external processing device and change an ANR setting specified by the first set of ANR settings to an ANR setting specified by the second set of ANR settings in response to the second set of ANR settings being received from the external processing device through the interface.

> In the method, above, changes to ANR settings may be made in a manner selected to maintain a selected quality of sound and/or selected quality of ANR, possibly while balancing the quality of sound and/or ANR with reducing power consumption. Analogously, in the apparatus above, the processing device may be caused to select changes in ANR

settings to maintain a selected quality of sound and/or selected quality of ANR, and the processing device may be caused to select the changes in the ANR settings to balance the quality of sound and/or ANR with reducing power consumption.

Other features and advantages of the invention will be apparent from the description and claims that follow.

# DESCRIPTION OF THE DRAWINGS

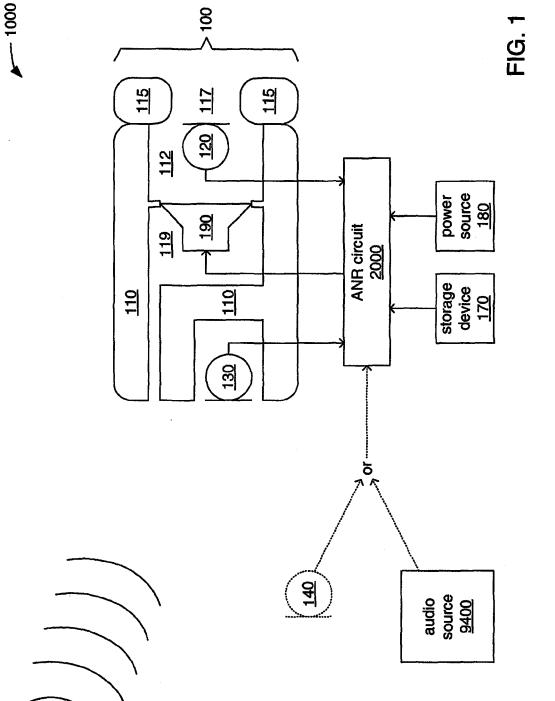

FIG. 1 is a block diagram of portions of an implementation of a personal ANR device.

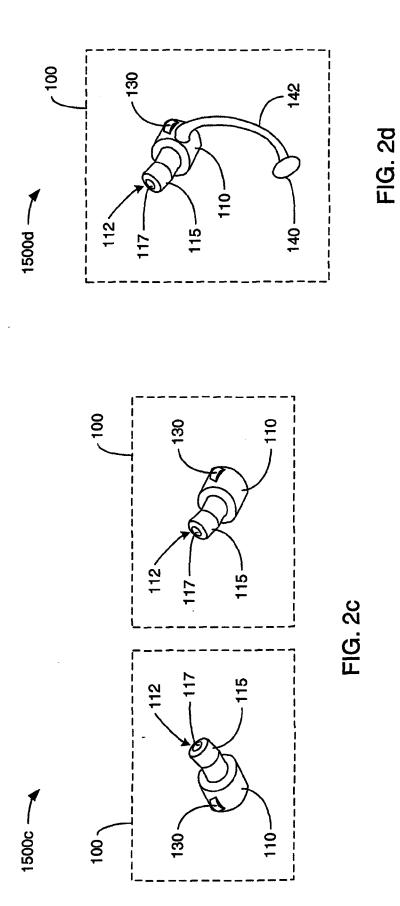

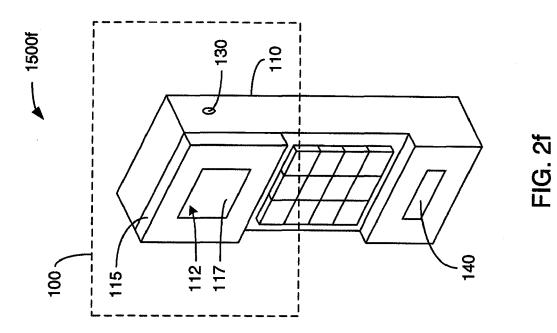

FIGS. 2a through 2f depict possible physical configurations of the personal ANR device of FIG. 1.

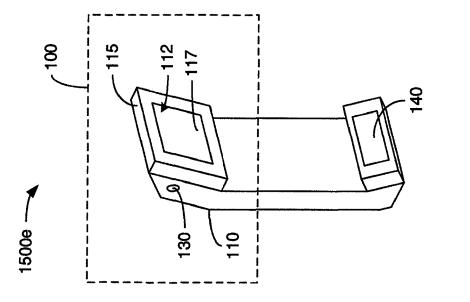

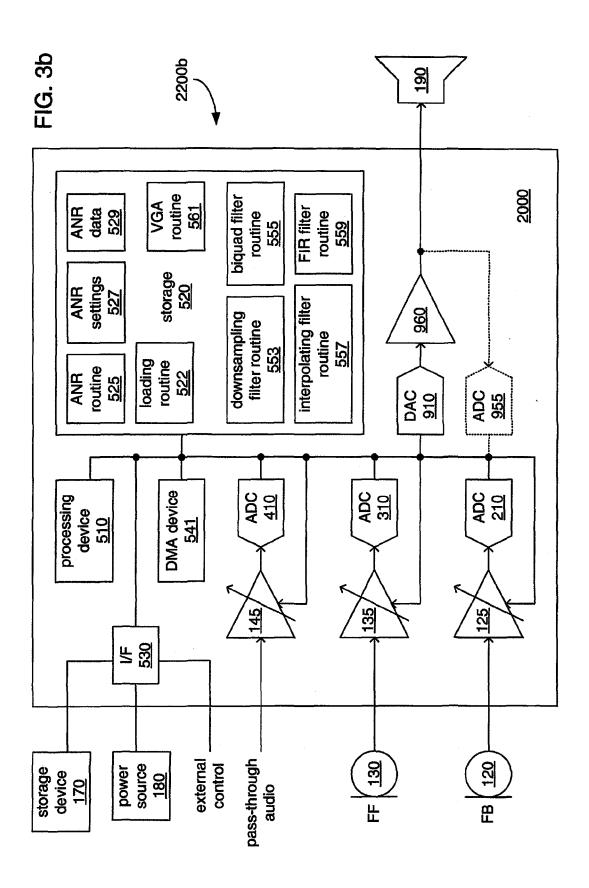

FIGS. 3a and 3b depict possible internal architectures of an ANR circuit of the personal ANR device of FIG. 1.

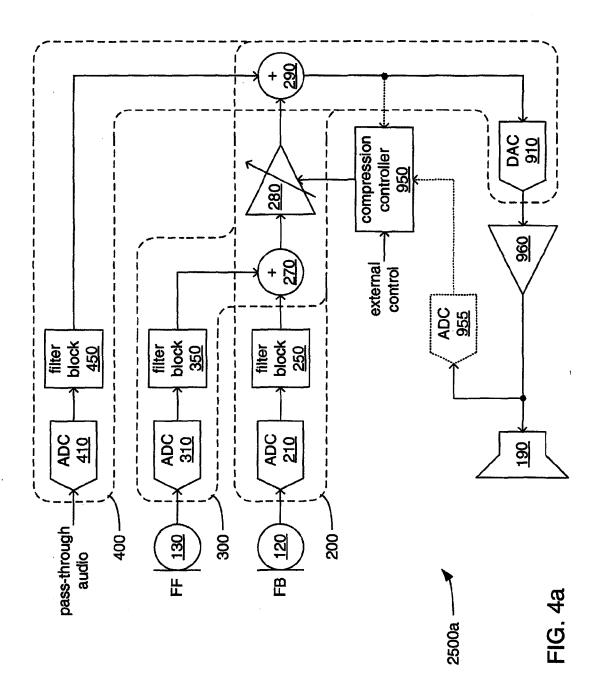

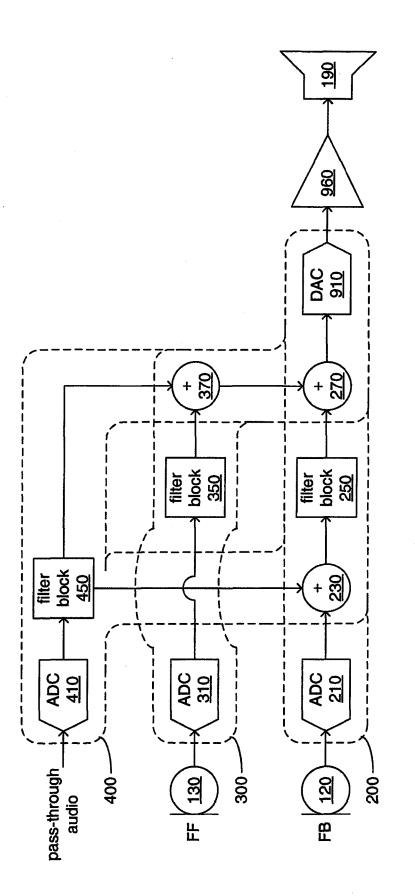

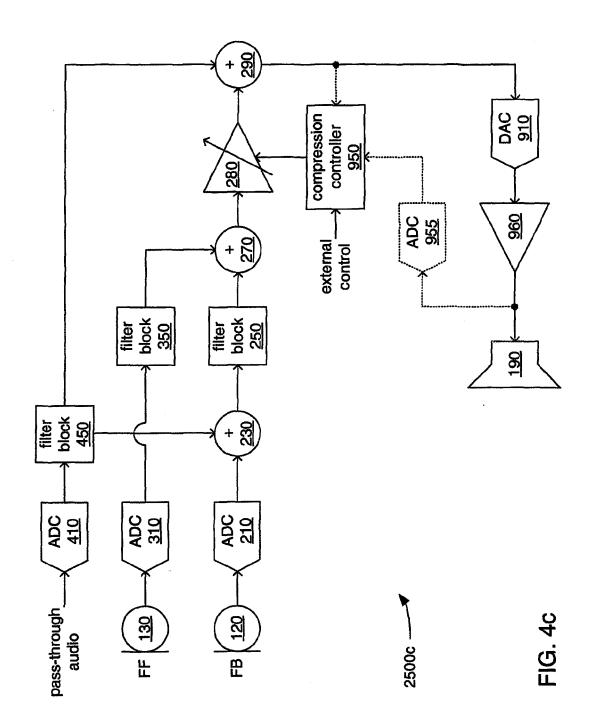

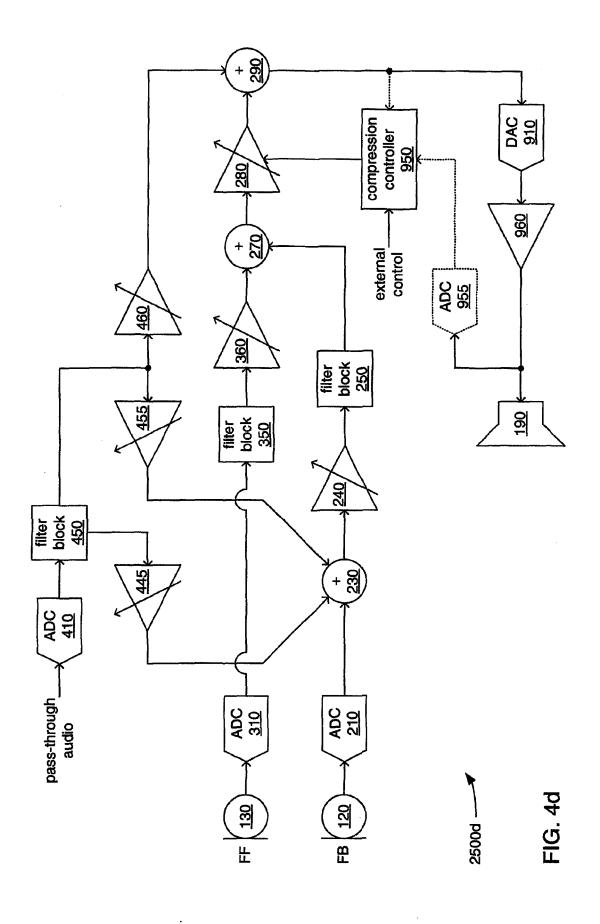

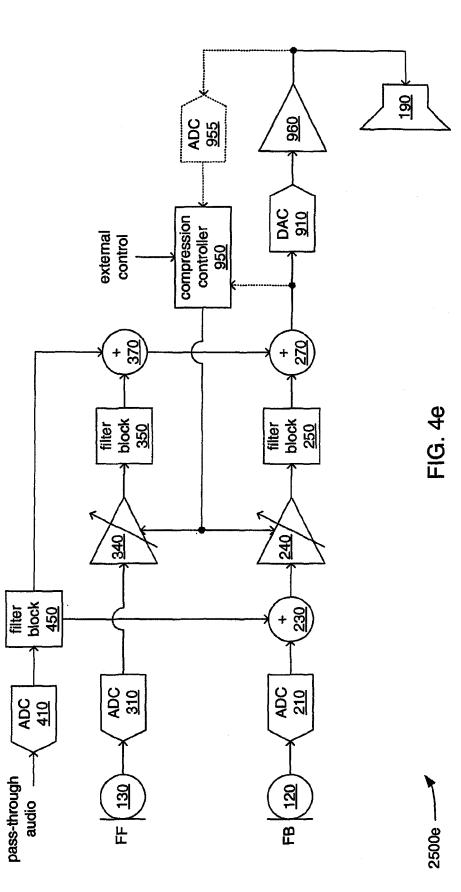

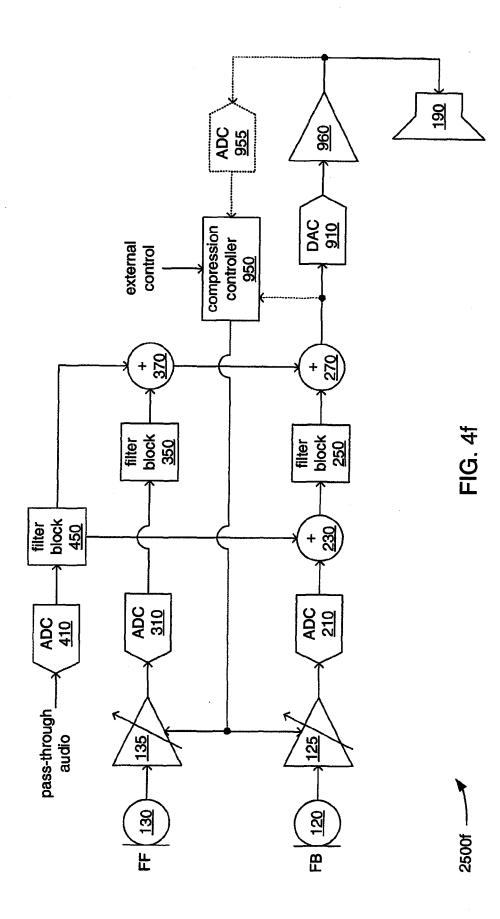

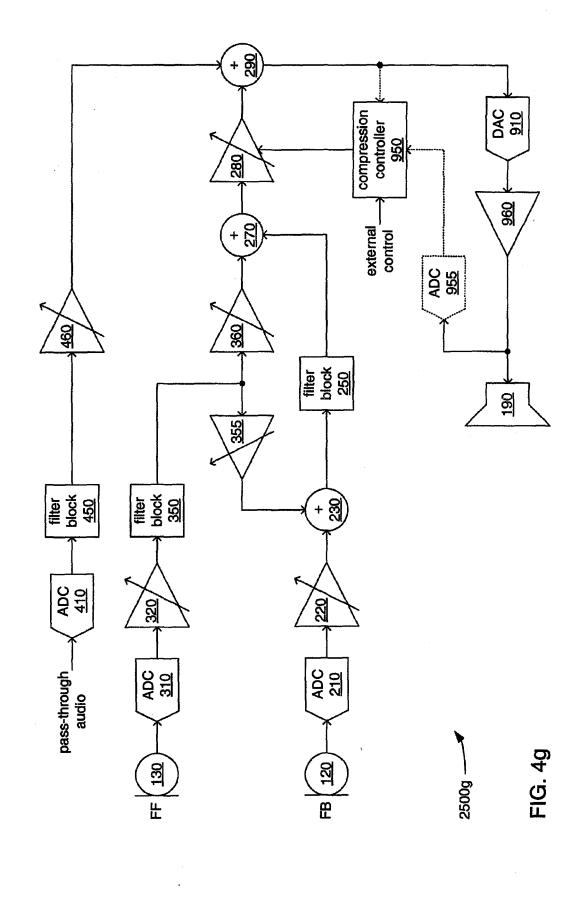

FIGS. 4a through 4g depict possible signal processing topologies that may be adopted by the ANR circuit of the personal ANR device of FIG. 1.

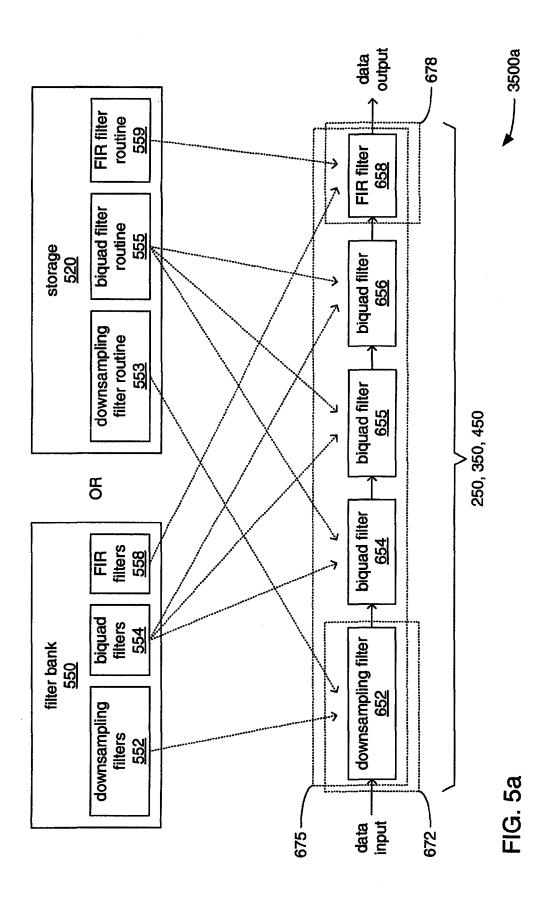

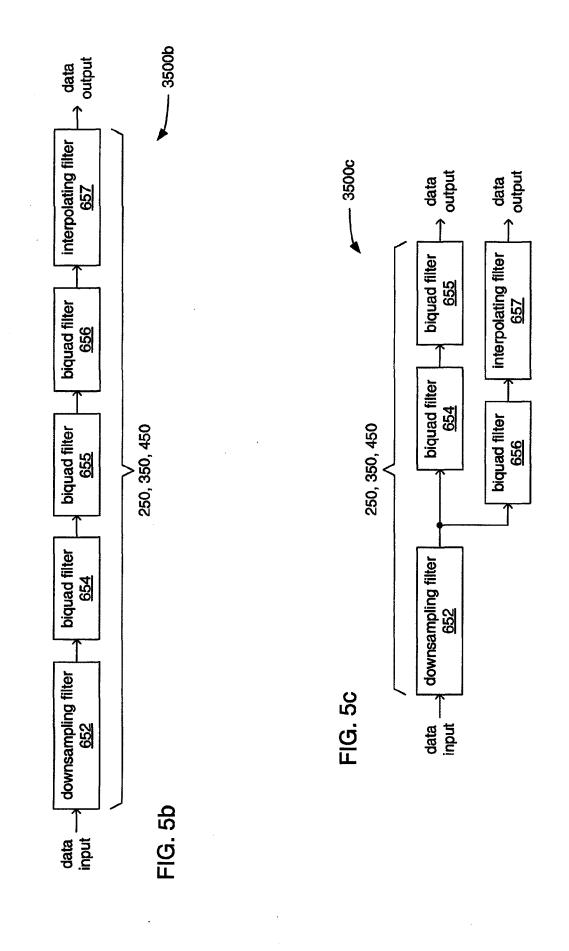

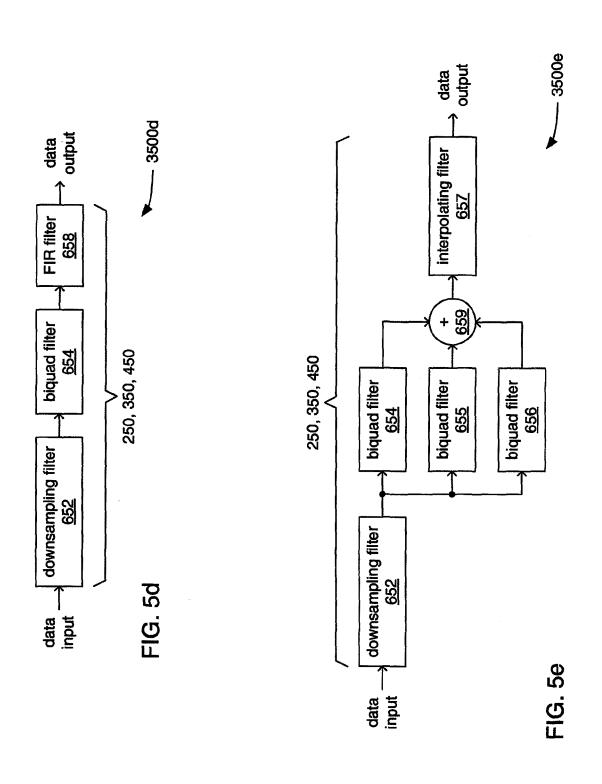

FIGS. 5*a* through 5*e* depict possible filter block topologies that may be adopted by the ANR circuit of the personal ANR device of FIG. 1.

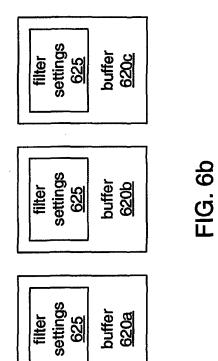

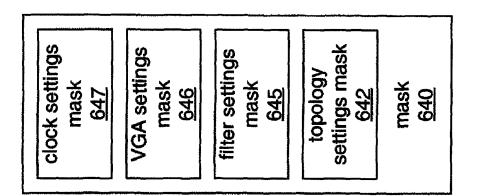

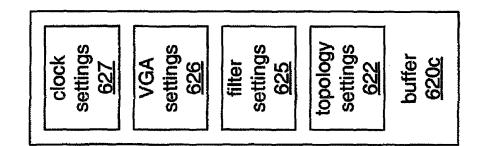

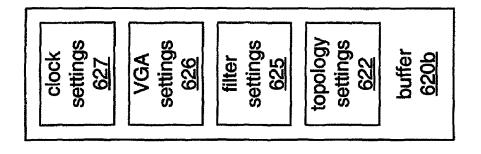

FIGS. 6a through 6c depict possible variants of triplebuffering that may be adopted by the ANR circuit of the 25 personal ANR device of FIG. 1.

# DETAILED DESCRIPTION

What is disclosed and what is claimed herein is intended to 30 be applicable to a wide variety of personal ANR devices, i.e., devices that are structured to be at least partly worn by a user in the vicinity of at least one of the user's ears to provide ANR functionality for at least that one ear. It should be noted that although various specific implementations of personal ANR 35 devices, such as headphones, two-way communications headsets, earphones, earbuds, wireless headsets (also known as "earsets") and ear protectors are presented with some degree of detail, such presentations of specific implementations are intended to facilitate understanding through the use 40 of examples, and should not be taken as limiting either the scope of disclosure or the scope of claim coverage.

It is intended that what is disclosed and what is claimed herein is applicable to personal ANR devices that provide two-way audio communications, one-way audio communi- 45 cations (i.e., acoustic output of audio electronically provided by another device), or no communications, at all. It is intended that what is disclosed and what is claimed herein is applicable to personal ANR devices that are wirelessly connected to other devices, that are connected to other devices 50 through electrically and/or optically conductive cabling, or that are not connected to any other device, at all. It is intended that what is disclosed and what is claimed herein is applicable to personal ANR devices having physical configurations structured to be worn in the vicinity of either one or both ears 55 of a user, including and not limited to, headphones with either one or two earpieces, over-the-head headphones, behind-theneck headphones, headsets with communications microphones (e.g., boom microphones), wireless headsets (i.e., earsets), single earphones or pairs of earphones, as well as 60 hats or helmets incorporating one or two earpieces to enable audio communications and/or ear protection. Still other physical configurations of personal ANR devices to which what is disclosed and what is claimed herein are applicable will be apparent to those skilled in the art.

Beyond personal ANR devices, what is disclosed and claimed herein is also meant to be applicable to the provision of ANR in relatively small spaces in which a person may sit or stand, including and not limited to, phone booths, car passenger cabins, etc.

ger cabins, etc. FIG. 1 provides a block diagram of a personal ANR device 5 1000 structured to be worn by a user to provide active noise reduction (ANR) in the vicinity of at least one of the user's ears. As will also be explained in greater detail, the personal ANR device 1000 may have any of a number of physical configurations, some possible ones of which are depicted in FIGS. 2a through 2f. Some of these depicted physical con-10 figurations incorporate a single earpiece 100 to provide ANR to only one of the user's ears, and others incorporate a pair of earpieces 100 to provide ANR to both of the user's ears. However, it should be noted that for the sake of simplicity of 15 discussion, only a single earpiece 100 is depicted and described in relation to FIG. 1. As will also be explained in greater detail, the personal ANR device 1000 incorporates at least one ANR circuit 2000 that may provide either or both of feedback-based ANR and feedforward-based ANR, in addition to possibly further providing pass-through audio. FIGS. 3a and 3b depict a couple of possible internal architectures of the ANR circuit 2000 that are at least partly dynamically configurable. Further, FIGS. 4a through 4e depict some possible signal processing topologies and FIGS. 5a through 5e depict some possible filter block topologies that may the ANR circuit 2000 may be dynamically configured to adopt. Further, the provision of either or both of feedback-based ANR and feedforward-based ANR is in addition to at least some degree of passive noise reduction (PNR) provided by the structure of each earpiece 100. Still further, FIGS. 6a through 6c depict various forms of triple-buffering that may be employed in dynamically configuring signal processing

topologies, filter block topologies and/or still other ANR settings. Each earpiece 100 incorporates a casing 110 having a cavity 112 at least partly defined by the casing 110 and by at least a portion of an acoustic driver 190 disposed within the casing to acoustically output sounds to a user's ear. This manner of positioning the acoustic driver 190 also partly defines another cavity 119 within the casing 110 that is separated from the cavity 112 by the acoustic driver 190. The casing 110 carries an ear coupling 115 surrounding an opening to the cavity 112 and having a passage 117 that is formed through the ear coupling 115 and that communicates with the opening to the cavity 112. In some implementations, an

5 opening to the cavity 112. In some implementations, an acoustically transparent screen, grill or other form of perforated panel (not shown) may be positioned in or near the passage 117 in a manner that obscures the cavity and/or the passage 117 from view for aesthetic reasons and/or to protect 0 components within the casing 110 from damage. At times when the earpiece 100 is worn by a user in the vicinity of one of the user's ears, the passage 117 acoustically couples the cavity 112 to the ear canal of that ear, while the ear coupling 115 engages portions of the ear to form at least some degree

5 of acoustic seal therebetween. This acoustic seal enables the casing 110, the ear coupling 115 and portions of the user's head surrounding the ear canal (including portions of the ear) to cooperate to acoustically isolate the cavity 112, the passage 117 and the ear canal from the environment external to the casing 110 and the user's head to at least some degree, thereby providing some degree of PNR.

In some variations, the cavity 119 may be coupled to the environment external to the casing 110 via one or more acoustic ports (only one of which is shown), each tuned by their dimensions to a selected range of audible frequencies to enhance characteristics of the acoustic output of sounds by the acoustic driver 190 in a manner readily recognizable to those skilled in the art. Also, in some variations, one or more tuned ports (not shown) may couple the cavities 112 and 119, and/or may couple the cavity 112 to the environment external to the casing 110. Although not specifically depicted, screens, grills or other forms of perforated or fibrous structures may be positioned within one or more of such ports to prevent passage of debris or other contaminants therethrough and/or to provide a selected degree of acoustic resistance therethrough.

In implementations providing feedforward-based ANR, a feedforward microphone 130 is disposed on the exterior of 10 the casing 110 (or on some other portion of the personal ANR device 1000) in a manner that is acoustically accessible to the environment external to the casing 110. This external positioning of the feedforward microphone 130 enables the feedforward microphone 130 to detect environmental noise 15 sounds, such as those emitted by an acoustic noise source 9900, in the environment external to the casing 110 without the effects of any form of PNR or ANR provided by the personal ANR device 1000. As those familiar with feedfordetected by the feedforward microphone 130 are used as a reference from which feedforward anti-noise sounds are derived and then acoustically output into the cavity 112 by the acoustic driver 190. The derivation of the feedforward antinoise sounds takes into account the characteristics of the PNR 25 entirely separate device from the personal ANR device 1000 provided by the personal ANR device 1000, characteristics and position of the acoustic driver 190 relative to the feedforward microphone 130, and/or acoustic characteristics of the cavity 112 and/or the passage 117. The feedforward antinoise sounds are acoustically output by the acoustic driver 30 190 with amplitudes and time shifts calculated to acoustically interact with the noise sounds of the acoustic noise source 9900 that are able to enter into the cavity 112, the passage 117 and/or an ear canal in a subtractive manner that at least attenuates them

In implementations providing feedback-based ANR, a feedback microphone 120 is disposed within the cavity 112. The feedback microphone 120 is positioned in close proximity to the opening of the cavity 112 and/or the passage 117 so as to be positioned close to the entrance of an ear canal when 40 the earpiece 100 is worn by a user. The sounds detected by the feedback microphone 120 are used as a reference from which feedback anti-noise sounds are derived and then acoustically output into the cavity 112 by the acoustic driver 190. The derivation of the feedback anti-noise sounds takes into 45 account the characteristics and position of the acoustic driver 190 relative to the feedback microphone 120, and/or the acoustic characteristics of the cavity 112 and/or the passage 117, as well as considerations that enhance stability in the provision of feedback-based ANR. The feedback anti-noise 50 sounds are acoustically output by the acoustic driver 190 with amplitudes and time shifts calculated to acoustically interact with noise sounds of the acoustic noise source 9900 that are able to enter into the cavity 112, the passage 117 and/or the ear canal (and that have not been attenuated by whatever 55 PNR) in a subtractive manner that at least attenuates them.

The personal ANR device 1000 further incorporates one of the ANR circuit 2000 associated with each earpiece 100 of the personal ANR device 1000 such that there is a one-to-one correspondence of ANR circuits 2000 to earpieces 100. Either 60 a portion of or substantially all of each ANR circuit 2000 may be disposed within the casing 110 of its associated earpiece 100. Alternatively and/or additionally, a portion of or substantially all of each ANR circuit 2000 may be disposed within another portion of the personal ANR device 1000. Depending 65 on whether one or both of feedback-based ANR and feedforward-based ANR are provided in an earpiece 100 associated

with the ANR circuit 2000, the ANR circuit 2000 is coupled to one or both of the feedback microphone 120 and the feedforward microphone 130, respectively. The ANR circuit 2000 is further coupled to the acoustic driver 190 to cause the acoustic output of anti-noise sounds.

In some implementations providing pass-through audio, the ANR circuit 2000 is also coupled to an audio source 9400 to receive pass-through audio from the audio source 9400 to be acoustically output by the acoustic driver 190. The passthrough audio, unlike the noise sounds emitted by the acoustic noise source 9900, is audio that a user of the personal ANR device 1000 desires to hear. Indeed, the user may wear the personal ANR device 1000 to be able to hear the pass-through audio without the intrusion of the acoustic noise sounds. The pass-through audio may be a playback of recorded audio, transmitted audio, or any of a variety of other forms of audio that the user desires to hear. In some implementations, the audio source 9400 may be incorporated into the personal ANR device 1000, including and not limited to, an integrated ward-based ANR will readily recognize, these sounds 20 audio playback component or an integrated audio receiver component. In other implementations, the personal ANR device 1000 incorporates a capability to be coupled either wirelessly or via an electrically or optically conductive cable to the audio source 9400 where the audio source 9400 is an (e.g., a CD player, a digital audio file player, a cell phone, etc.).

In other implementations pass-through audio is received from a communications microphone 140 integrated into variants of the personal ANR device 1000 employed in two-way communications in which the communications microphone 140 is positioned to detect speech sounds produced by the user of the personal ANR device 1000. In such implementations, an attenuated or otherwise modified form of the speech sounds produced by the user may be acoustically output to one or both ears of the user as a communications sidetone to enable the user to hear their own voice in a manner substantially similar to how they normally would hear their own voice when not wearing the personal ANR device 1000.

In support of the operation of at least the ANR circuit 2000, the personal ANR device 1000 may further incorporate one or both of a storage device 170, a power source 180 and/or a processing device (not shown). As will be explained in greater detail, the ANR circuit 2000 may access the storage device 170 (perhaps through a digital serial interface) to obtain ANR settings with which to configure feedback-based and/or feedforward-based ANR. As will also be explained in greater detail, the power source 180 may be a power storage device of limited capacity (e.g., a battery).

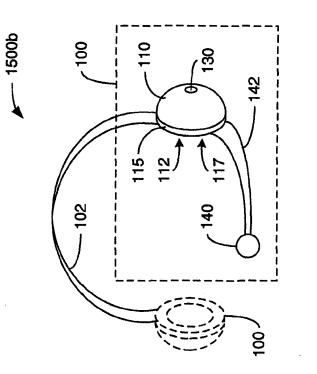

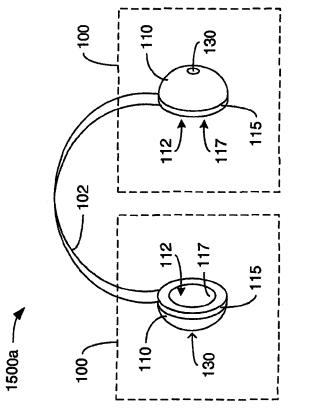

FIGS. 2a through 2f depict various possible physical configurations that may be adopted by the personal ANR device 1000 of FIG. 1. As previously discussed, different implementations of the personal ANR device 1000 may have either one or two earpieces 100, and are structured to be worn on or near a user's head in a manner that enables each earpiece 100 to be positioned in the vicinity of a user's ear.

FIG. 2a depicts an "over-the-head" physical configuration 1500a of the personal ANR device 1000 that incorporates a pair of earpieces 100 that are each in the form of an earcup, and that are connected by a headband 102. However, and although not specifically depicted, an alternate variant of the physical configuration 1500a may incorporate only one of the earpieces 100 connected to the headband 102. Another alternate variant of the physical configuration 1500a may replace the headband 102 with a different band structured to be worn around the back of the head and/or the back of the neck of a user.

10

In the physical configuration 1500*a*, each of the earpieces 100 may be either an "on-ear" (also commonly called "supraaural") or an "around-ear" (also commonly called "circumaural") form of earcup, depending on their size relative to the pinna of a typical human ear. As previously discussed, each earpiece 100 has the casing 110 in which the cavity 112 is formed, and that 110 carries the ear coupling 115. In this physical configuration, the ear coupling 115 is in the form of a flexible cushion (possibly ring-shaped) that surrounds the periphery of the opening into the cavity 112 and that has the passage 117 formed therethrough that communicates with the cavity 112.

Where the earpieces 100 are structured to be worn as overthe-ear earcups, the casing 110 and the ear coupling 115 cooperate to substantially surround the pinna of an ear of a user. Thus, when such a variant of the personal ANR device 1000 is correctly worn, the headband 102 and the casing 110 cooperate to press the ear coupling 115 against portions of a side of the user's head surrounding the pinna of an ear such 20 that the pinna is substantially hidden from view. Where the earpieces 100 are structured to be worn as on-ear earcups, the casing 110 and ear coupling 115 cooperate to overlie peripheral portions of a pinna that surround the entrance of an associated ear canal. Thus, when correctly worn, the head- 25 band 102 and the casing 110 cooperate to press the ear coupling 115 against portions of the pinna in a manner that likely leaves portions of the periphery of the pinna visible. The pressing of the flexible material of the ear coupling 115 against either portions of a pinna or portions of a side of a head 30 surrounding a pinna serves both to acoustically couple the ear canal with the cavity 112 through the passage 117, and to form the previously discussed acoustic seal to enable the provision of PNR.

FIG. 2b depicts another over-the-head physical configura- 35 tion 1500b that is substantially similar to the physical configuration 1500a, but in which one of the earpieces 100 additionally incorporates a communications microphone 140 connected to the casing 110 via a microphone boom 142. When this particular one of the earpieces 100 is correctly 40 worn, the microphone boom 142 extends from the casing 110 and generally alongside a portion of a cheek of a user to position the communications microphone 140 closer to the mouth of the user to detect speech sounds acoustically output from the user's mouth. However, and although not specifi- 45 cally depicted, an alternative variant of the physical configuration 1500b is possible in which the communications microphone 140 is more directly disposed on the casing 110, and the microphone boom 142 is a hollow tube that opens on one end in the vicinity of the user's mouth and on the other end in 50 the vicinity of the communications microphone 140 to convey sounds from the vicinity of the user's mouth to the vicinity of the communications microphone 140.

FIG. 2b also depicts the other of the earpieces 100 with broken lines to make clear that still another variant of the 55 physical configuration 1500b of the personal ANR device 1000 is possible that incorporates only the one of the earpieces 100 that incorporates the microphone boom 142 and the communications microphone 140. In such another variant, the headband 102 would still be present and would continue to be worn over the head of the user.

FIG. 2c depicts an "in-ear" (also commonly called "intraaural") physical configuration 1500c of the personal ANR device 1000 that incorporates a pair of earpieces 100 that are each in the form of an in-ear earphone, and that may or may 65 not be connected by a cord and/or by electrically or optically conductive cabling (not shown). However, and although not

specifically depicted, an alternate variant of the physical configuration 1500c may incorporate only one of the earpieces 100.

As previously discussed, each of the earpieces 100 has the casing 110 in which the open cavity 112 is formed, and that carries the ear coupling 115. In this physical configuration, the ear coupling 115 is in the form of a substantially hollow tube-like shape defining the passage 117 that communicates with the cavity 112. In some implementations, the ear coupling 115 is formed of a material distinct from the casing 110 (possibly a material that is more flexible than that from which the casing 110 is formed), and in other implementations, the ear coupling 115 is formed integrally with the casing 110.

Portions of the casing **110** and/or of the ear coupling **115** 15 cooperate to engage portions of the concha and/or the ear canal of a user's ear to enable the casing **110** to rest in the vicinity of the entrance of the ear canal in an orientation that acoustically couples the cavity **112** with the ear canal through the ear coupling **115**. Thus, when the earpiece **100** is properly 20 positioned, the entrance to the ear canal is substantially "plugged" to create the previously discussed acoustic seal to enable the provision of PNR.

FIG. 2d depicts another in-ear physical configuration 1500d of the personal ANR device 1000 that is substantially similar to the physical configuration 1500c, but in which one of the earpieces 100 is in the form of a single-ear headset (sometimes also called an "earset") that additionally incorporates a communications microphone 140 disposed on the casing 110. When this earpiece 100 is correctly worn, the communications microphone 140 is generally oriented towards the vicinity of the mouth of the user in a manner chosen to detect speech sounds produced by the user. However, and although not specifically depicted, an alternative variant of the physical configuration 1500d is possible in which sounds from the vicinity of the user's mouth are conveyed to the communications microphone 140 through a tube (not shown), or in which the communications microphone 140 is disposed on a boom (not shown) connected to the casing 110 and positioning the communications microphone 140 in the vicinity of the user's mouth.

Although not specifically depicted in FIG. 2d, the depicted earpiece 100 of the physical configuration 1500d having the communications microphone 140 may or may not be accompanied by another earpiece having the form of an in-ear earphone (such as one of the earpieces 100 depicted in FIG. 2c) that may or may not be connected to the earpiece 100 depicted in FIG. 2d via a cord or conductive cabling (also not shown).

FIG. 2e depicts a two-way communications handset physical configuration 1500e of the personal ANR device 1000 that incorporates a single earpiece 100 that is integrally formed with the rest of the handset such that the casing 110 is the casing of the handset, and that may or may not be connected by conductive cabling (not shown) to a cradle base with which it may be paired. In a manner not unlike one of the earpieces 100 of an on-the-ear variant of either of the physical configurations 1500a and 1500b, the earpiece 100 of the physical configuration 1500e carries a form of the ear coupling 115 that is configured to be pressed against portions of the pinna of an ear to enable the passage 117 to acoustically couple the cavity 112 to an ear canal. In various possible implementations, ear coupling 115 may be formed of a material distinct from the casing 110, or may be formed integrally with the casing 110.

FIG. 2f depicts another two-way communications handset physical configuration 1500f of the personal ANR device 1000 that is substantially similar to the physical configuration **1500***e*, but in which the casing **110** is shaped somewhat more appropriately for portable wireless communications use, possibly incorporating user interface controls and/or display(s) to enable the dialing of phone numbers and/or the selection of radio frequency channels without the use of a cradle base.

FIGS. 3a and 3b depict possible internal architectures, either of which may be employed by the ANR circuit 2000 in implementations of the personal ANR device 1000 in which the ANR circuit 2000 is at least partially made up of dynamically configurable digital circuitry. In other words, the inter- 10 nal architectures of FIGS. 3a and 3b are dynamically configurable to adopt any of a wide variety of signal processing topologies and filter block topologies during operation of the ANR circuit 2000. FIGS. 4a-g depict various examples of signal processing topologies that may be adopted by the ANR 15 circuit 2000 in this manner, and FIGS. 5a-e depict various examples of filter block topologies that may also be adopted by the ANR circuit 2000 for use within an adopted signal processing topology in this manner. However, and as those skilled in the art will readily recognize, other implementa- 20 tions of the personal ANR device 1000 are possible in which the ANR circuit 2000 is largely or entirely implemented with analog circuitry and/or digital circuitry lacking such dynamic configurability.

In implementations in which the circuitry of the ANR 25 circuit 2000 is at least partially digital, analog signals representing sounds that are received or output by the ANR circuit 2000 may require conversion into or creation from digital data that also represents those sounds. More specifically, in both of the internal architectures 2200a and 2200b, analog 30 signals received from the feedback microphone 120 and the feedforward microphone 130, as well as whatever analog signal representing pass-through audio may be received from either the audio source 9400 or the communications microphone 140, are digitized by analog-to-digital converters 35 (ADCs) of the ANR circuit 2000. Also, whatever analog signal is provided to the acoustic driver 190 to cause the acoustic driver 190 to acoustically output anti-noise sounds and/or pass-through audio is created from digital data by a digital-to-analog converter (DAC) of the ANR circuit 2000. 40 Further, either analog signals or digital data representing sounds may be manipulated to alter the amplitudes of those represented sounds by either analog or digital forms, respectively, of variable gain amplifiers (VGAs).

FIG. 3a depicts a possible internal architecture 2200a of 45 the ANR circuit 2000 in which digital circuits that manipulate digital data representing sounds are selectively interconnected through one or more arrays of switching devices that enable those interconnections to be dynamically configured during operation of the ANR circuit 2000. Such a use of 50 switching devices enables pathways for movement of digital data among various digital circuits to be defined through programming. More specifically, blocks of digital filters of varying quantities and/or types are able to be defined through which digital data associated with feedback-based ANR, 55 feedforward-based ANR and pass-through audio are routed to perform these functions. In employing the internal architecture 2200a, the ANR circuit 2000 incorporates ADCs 210, 310 and 410; a processing device 510; a storage 520; an interface (I/F) 530; a switch array 540; a filter bank 550; and 60 a DAC 910. Various possible variations may further incorporate one or more of analog VGAs 125, 135 and 145; a VGA bank 560; a clock bank 570; a compression controller 950; a further ADC 955; and/or an audio amplifier 960.

The ADC 210 receives an analog signal from the feedback 65 microphone 120, the ADC 310 receives an analog signal from the feedforward microphone 130, and the ADC 410 receives

an analog signal from either the audio source 9400 or the communications microphone 140. As will be explained in greater detail, one or more of the ADCs 210, 310 and 410 may receive their associated analog signals through one or more of the analog VGAs 125, 135 and 145, respectively. The digital outputs of each of the ADCs 210, 310 and 410 are coupled to the switch array 540. Each of the ADCs 210, 310 and 410 may be designed to employ a variant of the widely known sigmadelta analog-to-digital conversion algorithm for reasons of power conservation and inherent ability to reduce digital data representing audible noise sounds that might otherwise be introduced as a result of the conversion process. However, as those skilled in the art will readily recognize, any of a variety of other analog-to-digital conversion algorithms may be employed. Further, in some implementations, at least the ADC 410 may be bypassed and/or entirely dispensed with where at least the pass-through audio is provided to the ANR circuit 2000 as digital data, rather than as an analog signal.

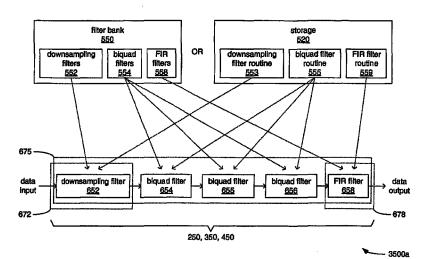

The filter bank 550 incorporates multiple digital filters, each of which has its inputs and outputs coupled to the switch array 540. In some implementations, all of the digital filters within the filter bank 550 are of the same type, while in other implementations, the filter bank 550 incorporates a mixture of different types of digital filters. As depicted, the filter bank 550 incorporates a mixture of multiple downsampling filters 552, multiple biquadratic (biquad) filters 554, multiple interpolating filters 556, and multiple finite impulse response (FIR) filters 558, although other varieties of filters may be incorporated, as those skilled in the art will readily recognize. Further, among each of the different types of digital filters may be digital filters optimized to support different data transfer rates. By way of example, differing ones of the biquad filters 554 may employ coefficient values of differing bitwidths, or differing ones of the FIR filters 558 may have differing quantities of taps. The VGA bank 560 (if present) incorporates multiple digital VGAs, each of which has its inputs and outputs coupled to the switch array 540. Also, the DAC 910 has its digital input coupled to the switch array 540. The clock bank 570 (if present) provides multiple clock signal outputs coupled to the switch array 540 that simultaneously provide multiple clock signals for clocking data between components at selected data transfer rates and/or other purposes. In some implementations, at least a subset of the multiple clock signals are synchronized multiples of one another to simultaneously support different data transfer rates in different pathways in which the movement of data at those different data transfer rates in those different pathways is synchronized.

The switching devices of the switch array 540 are operable to selectively couple different ones of the digital outputs of the ADCs 210, 310 and 410; the inputs and outputs of the digital filters of the filter bank 550; the inputs and outputs of the digital VGAs of the VGA bank 560; and the digital input of the DAC 910 to form a set of interconnections therebetween that define a topology of pathways for the movement of digital data representing various sounds. The switching devices of the switch array 540 may also be operable to selectively couple different ones of the clock signal outputs of the clock bank 570 to different ones of the digital filters of the filter bank 550 and/or different ones of the digital VGAs of the VGA bank 560. It is largely in this way that the digital circuitry of the internal architecture 2200a is made dynamically configurable. In this way, varying quantities and types of digital filters and/or digital VGAs may be positioned at various points along different pathways defined for flows of digital data associated with feedback-based ANR, feedforwardbased ANR and pass-through audio to modify sounds

represented by the digital data and/or to derive new digital data representing new sounds in each of those pathways. Also, in this way, different data transfer rates may be selected by which digital data is clocked at different rates in each of the pathways.

In support of feedback-based ANR, feedforward-based ANR and/or pass-through audio, the coupling of the inputs and outputs of the digital filters within the filter bank 550 to the switch array 540 enables inputs and outputs of multiple digital filters to be coupled through the switch array 540 to 10 create blocks of filters. As those skilled in the art will readily recognize, by combining multiple lower-order digital filters into a block of filters, multiple lower-order digital filters may be caused to cooperate to implement higher order functions without the use of a higher-order filter. Further, in implemen- 15 tations having a variety of types of digital filters, blocks of filters may be created that employ a mix of filters to perform a still greater variety of functions. By way of example, with the depicted variety of filters within the filter bank 550, a filter block (i.e., a block of filters) may be created having at least 20 one of the downsampling filters 552, multiple ones of the biquad filters 554, at least one of the interpolating filters 556, and at least one of the FIR filters 558.

In some implementations, at least some of the switching devices of the switch array 540 may be implemented with 25 binary logic devices enabling the switch array 540, itself, to be used to implement basic binary math operations to create summing nodes where pathways along which different pieces of digital data flow are brought together in a manner in which those different pieces of digital data are arithmetically summed, averaged, and/or otherwise combined. In such implementations, the switch array 540 may be based on a variant of dynamically programmable array of logic devices. Alternatively and/or additionally, a bank of binary logic devices or other form of arithmetic logic circuitry (not shown) 35 may also be incorporated into the ANR circuit 2000 with the inputs and outputs of those binary logic devices and/or other form of arithmetic logic circuitry also being coupled to the switch array 540.

In the operation of switching devices of the switch array 40 540 to adopt a topology by creating pathways for the flow of data representing sounds, priority may be given to creating a pathway for the flow of digital data associated with feedbackbased ANR that has as low a latency as possible through the switching devices. Also, priority may be given in selecting 45 digital filters and VGAs that have as low a latency as possible from among those available in the filter bank 550 and the VGA bank 560, respectively. Further, coefficients and/or other settings provided to digital filters of the filter bank 550 that are employed in the pathway for digital data associated 50 with feedback-based ANR may be adjusted in response to whatever latencies are incurred from the switching devices of the switch array 540 employed in defining the pathway. Such measures may be taken in recognition of the higher sensitivity of feedback-based ANR to the latencies of components 55 employed in performing the function of deriving and/or acoustically outputting feedback anti-noise sounds. Although such latencies are also of concern in feedforward-basedANR, feedforward-based ANR is generally less sensitive to such latencies than feedback-based ANR. As a result, a degree of 60 priority less than that given to feedback-based ANR, but greater than that given to pass-through audio, may be given to selecting digital filters and VGAs, and to creating a pathway for the flow of digital data associated with feedforward-based ANR.

The processing device 510 is coupled to the switch array 540, as well as to both the storage 520 and the interface 530.

The processing device 510 may be any of a variety of types of processing device, including and not limited to, a general purpose central processing unit (CPU), a digital signal processor (DSP), a reduced instruction set computer (RISC) processor, a microcontroller, or a sequencer. The storage 520 may be based on any of a variety of data storage technologies, including and not limited to, dynamic random access memory (DRAM), static random access memory (SRAM), ferromagnetic disc storage, optical disc storage, or any of a variety of nonvolatile solid state storage technologies. Indeed, the storage 520 may incorporate both volatile and nonvolatile portions. Further, it will be recognized by those skilled in the art that although the storage 520 is depicted and discussed as if it were a single component, the storage 520 may be made up of multiple components, possibly including a combination of volatile and nonvolatile components. The interface 530 may support the coupling of the ANR circuit 2000 to one or more digital communications buses, including digital serial buses by which the storage device 170 (not to be confused with the storage 520) and/or other devices external to the ANR circuit 2000 (e.g., other processing devices, or other ANR circuits) may be coupled. Further, the interface 530 may provide one or more general purpose input/output (GPIO) electrical connections and/or analog electrical connections to support the coupling of manually-operable controls, indicator lights or other devices, such as a portion of the power source 180 providing an indication of available power.

In some implementations, the processing device **510** accesses the storage **520** to read a sequence of instructions of a loading routine **522**, that when executed by the processing device **510**, causes the processing device **510** to operate the interface **530** to access the storage device **170** to retrieve one or both of the ANR routine **525** and the ANR settings **527**, and to store them in the storage **520**. In other implementations, one or both of the ANR routine **525** and the ANR settings **527** are stored in a nonvolatile portion of the storage **520** such that they need not be retrieved from the storage device **170**, even if power to the ANR circuit **2000** is lost.

Regardless of whether one or both of the ANR routine 525 and the ANR settings 527 are retrieved from the storage device 170, or not, the processing device 510 accesses the storage 520 to read a sequence of instructions of the ANR routine 525. The processing device 510 then executes that sequence of instructions, causing the processing device 510 to configure the switching devices of the switch array 540 to adopt a topology defining pathways for flows of digital data representing sounds and/or to provide differing clock signals to one or more digital filters and/or VGAs, as previously detailed. In some implementations, the processing device 510 is caused to configure the switching devices in a manner specified by a portion of the ANR settings 527, which the processing device 510 is also caused to read from the storage 520. Further, the processing device 510 is caused to set filter coefficients of various digital filters of the filter bank 550, gain settings of various VGAs of the VGA bank 560, and/or clock frequencies of the clock signal outputs of the clock bank 570 in a manner specified by a portion of the ANR settings 527.

In some implementations, the ANR settings **527** specify multiple sets of filter coefficients, gain settings, clock frequencies and/or configurations of the switching devices of the switch array **540**, of which different sets are used in response to different situations. In other implementations, execution of sequences of instructions of the ANR routine **525** causes the processing device **510** to derive different sets of filter coefficients, gain settings, clock frequencies and/or switching device configurations in response to different situations. By way of example, the processing device 510 may be caused to operate the interface 530 to monitor a signal from the power source 180 that is indicative of the power available from the power source 180, and to dynamically switch between different sets of filter coefficients, gain settings, clock frequencies and/or switching device configurations in response to changes in the amount of available power.

By way of another example, the processing device 510 may be caused to monitor characteristics of sounds represented by digital data involved in feedback-based ANR, feedforward- 10 based ANR and/or pass-through audio to determine whether or not it is desirable to alter the degree feedback-based and/or feedforward-based ANR provided. As will be familiar to those skilled in the art, while providing a high degree of ANR can be very desirable where there is considerable environ- 15 mental noise to be attenuated, there can be other situations where the provision of a high degree of ANR can actually create a noisier or otherwise more unpleasant acoustic environment for a user of a personal ANR device than would the provision of less ANR. Therefore, the processing device 510 20 may be caused to alter the provision of ANR to adjust the degree of attenuation and/or the range of frequencies of environmental noise attenuated by the ANR provided in response to observed characteristics of one or more sounds. Further, as will also be familiar to those skilled in the art, where a reduc- 25 tion in the degree of attenuation and/or the range of frequencies is desired, it may be possible to simplify the quantity and/or type of filters used in implementing feedback-based and/or feedforward-based ANR, and the processing device 510 may be caused to dynamically switch between different 30 sets of filter coefficients, gain settings, clock frequencies and/ or switching device configurations to perform such simplifying, with the added benefit of a reduction in power consumption.

The DAC 910 is provided with digital data from the switch 35 array 540 representing sounds to be acoustically output to an ear of a user of the personal ANR device 1000, and converts it to an analog signal representing those sounds. The audio amplifier 960 receives this analog signal from the DAC 910, and amplifies it sufficiently to drive the acoustic driver 190 to 40 effect the acoustic output of those sounds.

The compression controller 950 (if present) monitors the sounds to be acoustically output for an indication of their amplitude being too high, indications of impending instances of clipping, actual instances of clipping, and/or other impend- 45 ing or actual instances of other audio artifacts. The compression controller 150 may either directly monitor digital data provided to the DAC 910 or the analog signal output by the audio amplifier 960 (through the ADC 955, if present). In response to such an indication, the compression controller 50 950 may alter gain settings of one or more of the analog VGAs 125, 135 and 145 (if present); and/or one or more of the VGAs of the VGA bank 560 placed in a pathway associated with one or more of the feedback-based ANR, feedforward-based ANR and pass-through audio functions to adjust amplitude, 55 as will be explained in greater detail. Further, in some implementations, the compression controller 950 may also make such an adjustment in response to receiving an external control signal. Such an external signal may be provided by another component coupled to the ANR circuit 2000 to pro- 60 vide such an external control signal in response to detecting a condition such as an exceptionally loud environmental noise sound that may cause one or both of the feedback-based and feedforward-based ANR functions to react unpredictably.

FIG. 3b depicts another possible internal architecture 65 2200b of the ANR circuit 2000 in which a processing device accesses and executes stored machine-readable sequences of

instructions that cause the processing device to manipulate digital data representing sounds in a manner that can be dynamically configured during operation of the ANR circuit 2000. Such a use of a processing device enables pathways for movement of digital data of a topology to be defined through programming. More specifically, digital filters of varying quantities and/or types are able to be defined and instantiated in which each type of digital filter is based on a sequence of instructions. In employing the internal architecture 2200b, the ANR circuit 2000 incorporates the ADCs 210, 310 and 410; the processing device 510; the storage 520; the interface 530; a direct memory access (DMA) device 540; and the DAC 910. Various possible variations may further incorporate one or more of the analog VGAs 125, 135 and 145; the ADC 955; and/or the audio amplifier 960. The processing device 510 is coupled directly or indirectly via one or more buses to the storage 520; the interface 530; the DMA device 540; the ADCs 210, 310 and 410; and the DAC 910 to at least enable the processing device 510 to control their operation. The processing device 510 may also be similarly coupled to one or more of the analog VGAs 125, 135 and 145 (if present); and to the ADC 955 (if present).

As in the internal architecture 2200a, the processing device 510 may be any of a variety of types of processing device, and once again, the storage 520 may be based on any of a variety of data storage technologies and may be made up of multiple components. Further, the interface 530 may support the coupling of the ANR circuit 2000 to one or more digital communications buses, and may provide one or more general purpose input/output (GPIO) electrical connections and/or analog electrical connections. The DMA device 540 may be based on a secondary processing device, discrete digital logic, a bus mastering sequencer, or any of a variety of other technologies.

Stored within the storage 520 are one or more of a loading routine 522, an ANR routine 525, ANR settings 527, ANR data 529, a downsampling filter routine 553, a biquad filter routine 555, an interpolating filter routine 557, a FIR filter routine 559, and a VGA routine 561. In some implementations, the processing device 510 accesses the storage 520 to read a sequence of instructions of the loading routine 522, that when executed by the processing device 510, causes the processing device 510 to operate the interface 530 to access the storage device 170 to retrieve one or more of the ANR routine 525, the ANR settings 527, the downsampling filter routine 553, the biquad filter routine 555, the interpolating filter routine 557, the FIR routine 559 and the VGA routine 561, and to store them in the storage 520. In other implementations, one or more of these are stored in a nonvolatile portion of the storage 520 such that they need not be retrieved from the storage device 170.

As was the case in the internal architecture 2200a, the ADC 210 receives an analog signal from the feedback microphone 120, the ADC 310 receives an analog signal from the feedforward microphone 130, and the ADC 410 receives an analog signal from either the audio source 9400 or the communications microphone 140 (unless the use of one or more of the ADCs 210, 310 and 410 is obviated through the direct receipt of digital data). Again, one or more of the ADCs 210, 310 and 410 may receive their associated analog signals through one or more of the analog VGAs 125, 135 and 145, respectively. As was also the case in the internal architecture 2200a, the DAC 910 converts digital data representing sounds to be acoustically output to an ear of a user of the personal ANR device 1000 into an analog signal, and the audio amplifier 960 amplifies this signal sufficiently to drive the acoustic driver 190 to effect the acoustic output of those sounds.

However, unlike the internal architecture 2200a where digital data representing sounds were routed via an array of switching devices, such digital data is stored in and retrieved from the storage 520. In some implementations, the processing device 510 repeatedly accesses the ADCs 210, 310 and 5 410 to retrieve digital data associated with the analog signals they receive for storage in the storage 520, and repeatedly retrieves the digital data associated with the analog signal output by the DAC 910 from the storage 520 and provides that digital data to the DAC 910 to enable the creation of that 10 analog signal. In other implementations, the DMA device 540 (if present) transfers digital data among the ADCs 210, 310 and 410; the storage 520 and the DAC 910 independently of the processing device 510. In still other implementations, the ADCs 210, 310 and 410 and/or the DAC 910 incorporate "bus 15 mastering" capabilities enabling each to write digital data to and/or read digital data from the storage 520 independently of the processing device 510. The ANR data 529 is made up of the digital data retrieved from the ADCs 210, 310 and 410, and the digital data provided to the DAC 910 by the process-20 ing device 510, the DMA device 540 and/or bus mastering functionality.

The downsampling filter routine 553, the biquad filter routine 555, the interpolating filter routine 557 and the FIR filter that cause the processing device 510 to perform a combination of calculations that define a downsampling filter, a biquad filter, an interpolating filter and a FIR filter, respectively. Further, among each of the different types of digital filters may be variants of those digital filters that are opti- 30 mized for different data transfer rates, including and not limited to, differing bit widths of coefficients or differing quantities of taps. Similarly, the VGA routine 561 is made up of a sequence of instructions that cause the processing device 510 to perform a combination of calculations that define a VGA. 35 Although not specifically depicted, a summing node routine may also be stored in the storage 520 made up of a sequence of instructions that similarly defines a summing node

The ANR routine 525 is made up of a sequence of instructions that cause the processing device 510 to create a signal processing topology having pathways incorporating varying quantities of the digital filters and VGAs defined by the downsampling filter routine 553, the biquad filter routine 555, the interpolating filter routine 557, the FIR filter routine 559 and the VGA routine 561 to support feedback-based ANR, feedforward-based ANR and/or pass-through audio. The ANR routine 525 also causes the processing device 510 to perform the calculations defining each of the various filters and VGAs incorporated into that topology. Further, the ANR routine 525 either causes the processing device 510 to perform the moving of data among ADCs 210, 310 and 410, the storage 520 and the DAC 910, or causes the processing device 510 to coordinate the performance of such moving of data either by the DMA device 540 (if present) or by bus mastering operations performed by the ADCs 210, 310 and 410, and/or the 55 DAC 910.

The ANR settings 527 is made up of data defining topology characteristics (including selections of digital filters), filter coefficients, gain settings, clock frequencies, data transfer rates and/or data sizes. In some implementations, the topology characteristics may also define the characteristics of any summing nodes to be incorporated into the topology. The processing device 510 is caused by the ANR routine 525 to employ such data taken from the ANR settings 527 in creating a signal processing topology (including selecting digital fil- 65 ters), setting the filter coefficients for each digital filter incorporated into the topology, and setting the gains for each VGA

incorporated into the topology. The processing device 510 may be further caused by the ANR routine 525 to employ such data from the ANR settings 527 in setting clock frequencies and/or data transfer rates for the ADCs 210, 310 and 410; for the digital filters incorporated into the topology; for the VGAs incorporated into the topology; and for the DAC 910.