Exhibit 11

Smith Deposition Exh. 9

# United States Patent [19]

## Zdebel et al.

[11] Patent Number:

5,067,002

[45] Date of Patent:

Nov. 19, 1991

| [54] | INTEGRATED CIRCUIT STRUCTURES    |

|------|----------------------------------|

|      | HAVING POLYCRYSTALLINE ELECTRODE |

|      | CONTACTS                         |

| [75] | Inventors: | Peter J. Zdebel, Mesa; Raymond J. |

|------|------------|-----------------------------------|

|      |            | Balda, Tempe; Bor-Yuan Hwang,     |

|      |            | Chandler: Allen I Warman Dhan-i-  |

all of Ariz.

[73] Assignee: Motorola, Inc., Schaumburg, Ill.

[21] Appl. No.: 304,984

[22] Filed: Jan. 31, 1989

## Related U.S. Application Data

| [62] | Division of Ser. | No. | 9,322, | Jan. | 30, | 1987, | Pat. | No. |

|------|------------------|-----|--------|------|-----|-------|------|-----|

|      | 4,837,176.       |     |        |      |     |       |      |     |

|                    | 9/10 |

|--------------------|------|

| H01L 27/02; H01L 2 | 9/72 |

357/44; 357/45; 357/46; 357/46; 357/34;

## [56] References Cited

## U.S. PATENT DOCUMENTS

| Rc. 30,282 | 5/1980  | Hunt et al       | 148/15   |

|------------|---------|------------------|----------|

| 4,310,126  | 8/1978  | Bergeron et al   | 148/1.5  |

| 4,157,269  | 6/1979  | Ning et al.      | 357/59 H |

| 4,319,932  | 3/1982  | Jambotkar        | 148/15   |

| 4,324,038  | 4/1982  | Chang et al.     |          |

| 4,381,953  | 5/1983  | Ho et al.        |          |

| 4,430,793  | 2/1984  |                  |          |

| 4,443,932  | 4/1984  | Hart             |          |

| 4,445,967  | 5/1984  | Mastroanni et al |          |

| 4,483,726  |         | Kameyama         |          |

|            | 11/1984 | Isaac et al      |          |

| 4,495,010  | 1/1985  | Kranzer          |          |

| 4,516,316  | 5/1985  | Haskell          |          |

| 4,536,950  | 8/1985  | Sadamatsu et al  | 29/578   |

| 4,545,113  | 10/1985 | Vora             | 29/578   |

| 4,545,114  | 10/1985 | Ito et al.       | 29/579   |

| 4,581,319  | 4/1986  | Wieder et al     | 357/59 G |

| 4,590,666  | 5/1986  | Goto             |          |

| 4,593,453  | 6/1986  | Tam et al.       |          |

| 4,602,419  | 7/1986  | Harrison         |          |

| 4,602,421  | 7/1986  | Lee et al.       |          |

| 4,604,641  | 8/1986  |                  |          |

| 4,604,789  | 8/1986  | Konishi          |          |

| 4,608,589  | 8/1986  | Bourassa         |          |

| -,0,587    | 07 1380 | Goth et al       | 357/34   |

|            |         |                  |          |

| 4,611,384 | 9/1986  | Bencuya 29/571        |

|-----------|---------|-----------------------|

| 4,612,701 | 9/1986  | Cox                   |

| 4,640,721 | 2/1987  | Uehara et al 148/188  |

| 4,641,170 | 2/1987  | Ogura et al 357/35    |

| 4,641,416 | 2/1987  | Iranmesh et al 29/576 |

| 4,641,419 | 2/1987  | Kudo 29/591           |

| 4,648,909 | 3/1987  | Krishna 148/15        |

| 4,659,428 | 4/1987  | Maas et al 357/59     |

| 4,689,872 |         | Appels et al 437/228  |

| 4,712,125 | 12/1987 | Bhatia et al 357/59 H |

## FOREIGN PATENT DOCUMENTS

|          |        | European Pat. Off. ,       |

|----------|--------|----------------------------|

| 0090963  | 3/1983 | European Pat. Off 357/59   |

| 0137906  | 8/1984 | European Pat. Off 357/23.4 |

| 60-16189 | 6/1986 | Japan .                    |

## OTHER PUBLICATIONS

Jambotkar et al., "Reducing the device size of polysilicon base transistor", IBM Tech. Bull.; 12/82, vol. 25, No. 7B, pp. 4011-4015.

#### (List continued on next page.)

Primary Examiner—Rolf Hille

Assistant Examiner—Wael Fahmy

Attorney, Agent, or Firm—Robert M. Handy; Eugene A.

Parsons

#### [57] ABSTRACT

A process is disclosed for fabricating improved integrated circuit devices. In accordance with one embodiment of the invention integrated devices are fabricated by a process which produces small device areas without relying upon restrictive photolithography tolerances. The process uses four polycrystalline silicon layers to fabricate and contact the device regions, to achieve a relatively planar structure, and to reduce the size of device regions below normal photolithographic tolerances. The process uses a master mask to define the basic footprint of the device in combination with easy to align block-out masks in each lithography step. Means and methods for many types of devices such as complementary lateral and vertical bipolar transistors, JFETs, Sits, MOSFETs, resistors, diodes, capacitors and other devices which can be simultaneously fabricated are also described.

## 20 Claims, 46 Drawing Sheets

the oxidation mask. This portion of the process is well known in the art. Any convenient method of producing isolation walls may be used.

Epi-islands 80 and 82 or equivalent may be used for a variety of device regions besides the collector region 5 and emitter/base regions of the NPN transistor being described here. Examples of the use of such epi-islands for other device regions will be provided later and those of skill in the art will appreciate that the description herein is by way of example and not intended to be 10 limiting.

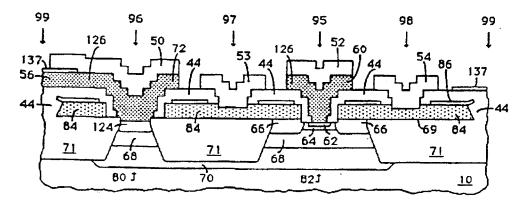

The surface of epi-region 68 is cleaned to avoid the formation of undesirable interfacial oxide between the epi-layer and layer 84 of polycrystalline semiconductor which will be subsequently deposited. Following cleaning, a series of layers are deposited on surface 69 of epi-region 68 and oxide region 71, as illustrated in FIG. 3. FIG. 3 shows a schematic cross-section corresponding to FIGS. 2, but at an earlier stage of fabrication.

Two layers 84, 86 are conveniently deposited on 20 surface 69 using low pressure chemical vapor deposition (LPCVD). First layer 84 is a layer of polycrystalline semiconductor, preferably silicon having a thickness conveniently of about 385 nanometers. Larger or smaller thicknesses may be used for layer 84 according 25 to relationships with other layers which will be subsequently explained. Second layer 86 is conveniently a layer of silicon nitride or a sandwich of oxide plus nitride or a layer of other oxidation resistant material having a thickness of, for example, about 70-120 nano- 30 meters. Poly silicon layer 84 will be used to form poly silicon base contact regions 84 of FIG. 2. Where an NPN transistor is being formed, layer 84 is doped by ion implantation of, for example, boron. The doping may be performed during or anytime after deposition of layer 35 84, but is conveniently performed after deposition of layers 84 and 86 through nitride layer 86 and before deposition of layers 88 or 90. Poly silicon layer 84 is conveniently doped with singly ionized boron at an energy of about 70 KeV to a dose of about 1×1016 40 2, although other doping levels may also be used depending on the desired device and circuit characteristics. The implantation is preferably arranged so that the relatively high dose of boron is located near the upper surface of polycrystalline silicon layer 84, just below 45 silicon nitride 86

After the boron implantation, two further layers 88, 90 are deposited, for example by LPCVD, over silicon nitride layer 86. Layer 88 is desirably an undoped layer of polycrystalline silicon having a thickness conveniently of about 180 nanometers. Larger or smaller thicknesses may be used for layer 88, taking into account the thickness of other layers, as will be subsequently explained. Layer 90 is formed overlying poly layer 88. Layer 90 conveniently prevents contamination 55 of poly layer 88 and serves as a hard mask for subsequent lithographic patterning of the underlying layers. Layer 90 may be of any material suitable for such purposes. Layer 90 is conveniently of silicon oxide having a thickness of about 20-40 nanometers.

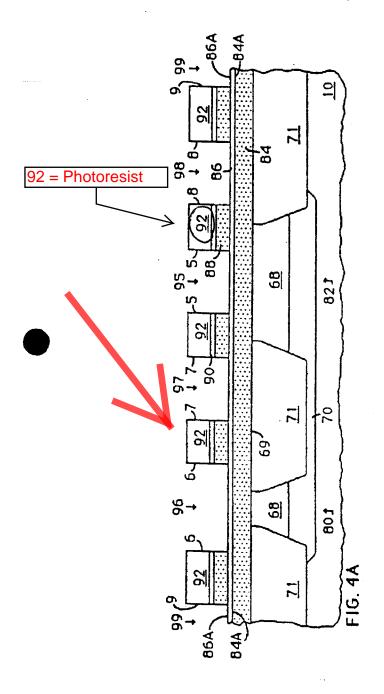

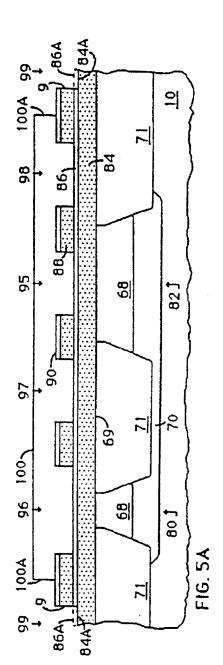

Processing of the structure continues with the application of layer 92 of photoresist overlying oxide layer 90 as shown schematically in FIG. 4A. The photoresist is patterned using master mask 94, represented by the shaded region in FIG. 4B, containing images 95-99 for 65 locating various device regions. Master mask 94 provides self-alignment of the critical device areas, for example in the case of the vertical NPN transistor, the

collector contact, the base contact or contacts, the emitter contact, and the emitter-base active region. In accordance with one embodiment of the invention, master mask 94 defines the master electrode area which includes emitter contact opening 95, collector contact opening 96, and base contact openings 97, 98 located within perimeter 9 and surrounded by external region 99. Region 99 identifies the region, outside perimeter 9 of master mask 94. Openings or windows 95-98 located within perimeters 5-8 respectively are used in the subsequent process to form the "footprints" of the device terminals, and in the case of the vertical bipolar device, the active emitter-base region. Perimeter 5, although referred to generally herein as the emitter opening or emitter contact opening, is used in conjunction with epitaxial island 82 formed within field oxide 71 to locate both the base and emitter of the device as well as the emitter contact. Variations and further embodiments, in addition to the basic NPN transistor, are discussed later. Base contact openings 97, 98 are located within perimeters 7, 8 respectively. Collector contact opening 96 is located within perimeter 6.

Master mask 94 is aligned to epi-islands 80, 82 as shown in FIG. 4B. In a preferred embodiment, the minimum geometry of any feature included in the master mask is a dimension, such as for example, about 1.5 micrometers, which can be processed easily with standard photolithography alignment tools. As will become apparent, fine geometry devices having features less than the minimum geometry size can be readily produced by the inventive process and structure without resorting to more difficult photolithography. The process may be readily scaled to smaller dimensions as lithographic and process resolution improve.

A particular feature of the present invention is that the master mask automatically self-aligns the emitter, base, and collector contacts and outer device periphery, so that, when metal is subsequently applied thereto, only one alignment tolerance (master mask to metal mask) need be accommodated. This allows devices having smaller metal pitch and therefore smaller overall size to be constructed as compared to the prior art processes which do not provide such self-alignment of the emitter, base, and collector contacts and the device periphery. As will be subsequently explained, other device types may be built on the same substrate using the same basic process sequence described herein, and they will also have the same minimum pitch advantage. As will be further explained, part of the self-alignment feature may be sacrificed to gain other advantages. These trade-offs are particularly noted.

Using master mask 94 to expose photoresist layer 92, the process continues by defining master mask pattern 94 in photoresist layer 92 and subsequently in layers 90 and 88, as illustrated schematically in FIG. 4A.

Photoresist is an organic material and has a potential for contaminating other parts of the process. Accordingly, in a preferred process the resist is used only to pattern layer 90 and then is removed. When layer 90 is 60 of oxide it is conveniently patterned using wet chemical etchants such as a 10:1 solution of ammonium fluoride and hydrofluoric acid or by reactive ion etching. Other etching means well known in the art may also be used. For further etching it is desirable to use a differential 65 etching process which attacks polysilicon layer 88 more rapidly than mask layer 90 or underlying nitride layer 86. Polysilicon layer 88 is subsequently patterned by reactive ion etching or other suitable differential etch-