# IN THE UNITED STATES DISTRICT COURT

# FOR THE WESTERN DISTRICT OF WISCONSIN

# SEMICONDUCTOR ENERGY LABORATORY CO., LTD.,

Plaintiff,

## OPINION AND ORDER

v.

09-cv-01-bbc

SAMSUNG ELECTRONICS CO., LTD., S-LCD CORPORATION, SAMSUNG ELECTRONICS AMERICA, INC., SAMSUNG TELECOMMUNICATIONS AMERICA, LLC and SAMSUNG MOBILE DISPLAY CO., LTD.,

Defendants.

In this patent infringement lawsuit, plaintiff Semiconductor Energy Laboratory Company, Ltd. contends that certain liquid crystal display products made by defendants Samsung Electronics Company, Ltd., S-LCD Corporation, Samsung Electronics America, Inc., Samsung Telecommunications America, LLC and Samsung Mobile Display Co., Ltd. infringe four of plaintiff's patents relating to thin-film transistors: U.S. Patents Nos. 6,900,463 (the '463 patent), 7,215,402 (the '402 patent), 7,394,516 (the '516 patent) and 7,413,937 (the '937 patent). Defendants have filed counterclaims, alleging that the patentsin-suit are invalid and they have asserted several affirmative defenses.

Before the court are the parties' cross motions for partial summary judgment on plaintiff's claims that the accused products infringe the '463 patent and on all defendants' invalidity, patent prosecution laches and inequitable conduct defenses regarding the four patents-in-suit. Dkt. ##201 and 202. This opinion addresses only the parties' arguments with respect to infringement of the '463 patent and to invalidity as it relates to anticipation and obviousness only. The parties' motions on defendants' remaining defenses, including invalidity of the '463 patent for inequitable conduct and the invalidity of the asserted claims of the '402, '516 and '937 patents as anticipated or rendered obvious, will be the subject of a separate opinion.

With respect to infringement of the '463 patent, defendants have moved for summary judgment on all 14 asserted claims; plaintiff seeks summary judgment on claims 1 and 5. Defendants' motion for summary judgment on noninfringement of the '463 patent will be denied. Plaintiff's motion for summary judgment on infringement is denied in part and granted with respect to the following questions:

1. Whether the accused products satisfy the requirement in claims 1-7 and 12-13 that the channel region be "in contact" with the source and drain regions;

- Whether the accused products satisfy the requirement in claims 1, 5, 12 and 13 that the accused channel region be located "between" the source and drain regions;

- 3. Whether the accused products satisfy the element of claims 8, 9, and 14 requiring the claimed thin film transistor to have "a semiconductor film having at least a source, drain and channel region";

- 4. Whether the accused products satisfy the requirement in claims 1-4, 8-12 and 14 that the channel region form junctions with the source and drain regions; and

- 5. Whether the accused products satisfy the non-single crystal semiconductor element of claims 1 and 5.

Plaintiff's motion for summary judgment will be denied with respect to the other elements of claims 1-14 of the '463 patent because material issues of fact remain in dispute. To be specific, it will be left to the jury to determine whether the accused products satisfy the requirements in claims 5 and 13 that the channel region (1) forms PI or NI junctions with the source and drain regions and (2) is comprised of an intrinsic amorphous silicon semiconductor material.

With respect to invalidity of the '463 patent, defendants base their motion for summary judgment on their assertions that the asserted claims are anticipated or rendered obvious by Sakamoto, rendered obvious in light of Matsumura and LeComber and rendered obvious in light of Matsumura and Sakamoto. Plaintiff has moved for summary judgment on defendants' claims that the '463 patent claims are anticipated by Sakamoto, Kazmerski and JP '663 and '664.

The material issues of fact in dispute about whether Sakamoto discloses the "recombination center neutralizer" and "intrinsic channel region" elements of the '463 patent prevent me from deciding as a matter of law whether Sakamoto anticipates the '463 patent or renders it obvious. Therefore, I will deny the parties' motions for summary judgment on those issues. For the same reason, I will deny defendants' motion for summary judgment on the obviousness of the '463 patent in light of Matsumura and LeComber or Sakamoto. In light of the parties' factual disputes relating to obviousness, I decline to address plaintiff's arguments of secondary obviousness considerations.

Plaintiff's motion for summary judgment will be granted with respect to defendants' claim that the '463 patent is invalid as anticipated by Kazmerski because defendants have failed to show that it would have been obvious to combine two different embodiments appearing in that reference. Plaintiff's motion for summary judgment on defendants' claim that the '463 patent is invalid as anticipated by JP '663 and '664 will be denied. The following questions remain to be decided at trial:

- 1. Whether the '463 patent is anticipated or rendered obvious by Sakamoto;

- 2. Whether JP '663 and '664 anticipates the '463 patent; and

3. Whether the combination of Matsumura and LeComber or Matsumura and Sakamoto render the '463 patent claims obvious;

For the purpose of deciding the parties' motions for summary judgment on infringement and invalidity of the '463 patent, I find that the following facts are undisputed and material.

## UNDISPUTED FACTS

# A. The Parties

Plaintiff Semiconductor Energy Laboratory Co. Ltd. is a Japanese corporation. Defendants Samsung Electronics Company, Ltd., S-LCD Corporation and Samsung Mobile Display Co., Ltd. are Korean corporations. Defendants Samsung Electronics America, Inc. and Samsung Telecommunications America, LLC are American corporations. Defendants manufacture a large number of consumer electronic products that include televisions, laptop computers, computer monitors and cell phones. Until 2005, defendants manufactured thin film transistors under an express written license with plaintiff.

## B. <u>General Technology</u>

Liquid crystal displays (LCD) modules or panels, including those in the accused products, incorporate thin film transistors containing amorphous silicon semiconductor material. Each LCD is divided into thousands (or millions) of tiny picture elements called "pixels," which form the image on the LCD screen. Increasing the number of pixels in a given area produces a higher resolution picture. A high-definition LCD has more pixels than a standard-definition screen of the same size. The color and brightness of each pixel is determined by even smaller elements in the LCD called sub-pixels, each of which is associated with a thin film transistor that works as an electronic switch.

An LCD is a multilayered "sandwich" consisting of at least a backlight, a thin film transistor substrate, liquid crystal material, a counter substrate, a seal, and driver circuitry. The **backlight** is the LCD's light source. A **thin film transistor substrate** contains an array of thousands of thin film transistors that work as electric "switches" to control the electric current going to each individual pixel. The thin film transistors effectively turn individual pixels on and off and vary the brightness and intensity of individual pixels to help create colors. **Liquid crystal material** is located between the thin film transistor substrate and the counter substrate; it affects the display of light from the backlight. A **counter substrate** is fitted with color filters that determine the colors to be displayed. Each pixel has three sub-pixels, each corresponding to a different color filter, typically, red, green and blue, on the counter substrate. The amount of light that passes through each sub-pixel determines the color of the pixel. The **seal** is an adhesive material that binds the thin film transistor and counter substrates together, enclosing the liquid crystal material and LCD components and

preventing impurities from entering the device. **Driver circuitry** is attached to or on the thin film transistor substrate and sends signals to control the thin film transistors.

Plaintiff's expert, Professor Tsu-Jae King Liu, identified the accused products by product code, module code, panel code, product ID and mask design code. The following chart generally summarizes certain Samsung manufacturing lines, facilities, panel sizes and products:

| Fabrication | Generation | Panel Size(s) (inches)                              | Product     |

|-------------|------------|-----------------------------------------------------|-------------|

| Facility    | Line       |                                                     |             |

| Chonan      | L3         | 10.6, 12.1, 13.3, 14, 14.1                          | Notebook PC |

| Chonan      | L4         | 12.1, 14.1, 15, 15.4                                | Notebook PC |

| Chonan      | L4         | 21.3, 30                                            | Monitor     |

| Chonan      | L5         | 8.9, 10.1, 13.3, 13.4, 14, 15, 15.4, 15.6, 17.3     | Notebook PC |

| Chonan      | L5         | 15, 17, 19, 20, 24, 27                              | Monitor     |

| Chonan      | L6         | 11.6, 12.1, 13.3, 14, 14.1, 15, 15.4, 16, 17, 18.4, | Notebook PC |

|             |            | 19                                                  |             |

| Chonan      | L6         | 17, 18.5, 19, 20.1, 21, 22                          | Monitor     |

| Tanjung     | T7-1       | 32, 40, 46                                          | Television  |

| Tanjung     | T7-2       | 17, 19, 20, 22, 23, 24, 26, 27                      | Monitor     |

| Tanjung     | T7-2       | 26, 32, 40, 46, 52, 57, 70, 82                      | Television  |

| Tanjung     | T8-1       | 18.5, 21.5, 22                                      | Monitor     |

| Tanjung     | T8-1       | 21.6, 32, 46, 52, 55                                | Television  |

| Tanjung     | T8-2       | 32, 46, 52                                          | Television  |

# C. The '463 Patent Claims

On May 31, 2005, the '463 patent was issued to plaintiff Semiconductor Energy Laboratory Company, Ltd. for an invention entitled "Semiconductor Device," which describes the manufacturing steps of a thin film transistor. The '463 patent indicates that the patent application was filed on September 8, 1992 and claims priority to Japanese Patent Application 55-88975 filed on June 30, 1980. It names Shunpei Yamazaki and Yujiro

Nagata as inventors. The '463 patent recites the following claims:

1. A thin film transistor comprising:

a pair of source and drain regions;

a channel region between said source and drain regions; and

a gate electrode adjacent to said channel region with a gate insulating film interposed therebetween, said channel region comprising an amorphous silicon semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof;

said pair of source and drain regions comprising a non-single crystal semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof, and having an impurity conductivity type to form junctions in contact with said channel region,

wherein at least a portion of said gate insulating film which is in direct contact with said channel region comprises a nitride.

2. A thin film transistor according to claim 1 wherein said channel region has an intrinsic conductivity type.

\* \* \*

5. A thin film transistor comprising:

a pair of source and drain regions;

a channel region between said source and drain regions; and

a gate electrode adjacent to said channel region with a gate insulating film

interposed therebetween,

said channel region comprising an intrinsic amorphous silicon semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof;

said pair of source and drain regions comprising a non-single crystal semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof, and having a P or N type conductivity to form PI or NI junctions in contact with said channel region,

wherein at least a portion of said gate insulating film which is in direct contact with said channel region comprises a nitride.

\* \* \*

8. A thin film transistor comprising:

a semiconductor film having at least source, drain and channel regions comprising amorphous silicon, said source and drain regions forming junctions with said channel region;

a gate insulating film adjacent to said channel region; and

a gate electrode adjacent to said channel region with said gate insulating film therebetween,

wherein said amorphous silicon semiconductor film contains a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof, and at least a portion of said gate insulating film which is in contact with said channel region comprises a nitride.

9. A thin film transistor according to claim 8 wherein said channel region has an intrinsic conductivity type.

\* \* \*

12. A thin film transistor comprising:

a pair of source and drain regions;

a channel region between said source and drain regions; and

a gate electrode adjacent to said channel region with a gate insulating film interposed therebetween,

said channel region comprising an amorphous silicon semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof;

said pair of source and drain regions comprising a non-single crystal semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof, and having an impurity conductivity type to form junctions in contact with said channel region,

wherein at least a portion of said gate insulating film which is in direct contact with said channel region comprises a nitride;

wherein said channel region is interposed between said gate insulating film and another insulator different from said gate insulating film; and

wherein at least a portion of said junctions are covered by said another insulator.

13. A thin film transistor comprising:

a pair of source and drain regions;

a channel region between said source and drain regions; and

a gate electrode adjacent to said channel region with a gate insulating film interposed therebetween,

said channel region comprising an intrinsic amorphous silicon semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof;

said pair of source and drain regions comprising a non-single crystal semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof, and having a P or N type conductivity to form PI or NI junctions in contact with said channel region,

wherein at least a portion of said gate insulating film which is in direct contact with said channel region comprises a nitride; and

wherein said channel region is interposed between said gate insulating film and another insulator different from said gate insulating file; and

wherein at least a portion of said junctions are covered by said another insulator.

14. A thin film transistor comprising:

a semiconductor film having at least source, drain and channel regions comprising amorphous silicon, said source and drain regions forming junctions with said channel region;

a gate insulating film adjacent to said channel region; and

a gate electrode adjacent to said channel region with said gate insulating film therebetween,

wherein said amorphous silicon semiconductor film contains a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof, and at least a portion of said gate insulating film which is in contact with said channel region comprises a nitride; and

wherein said channel region is interposed between said gate insulating film and another insulator different from said gate insulating film; and

wherein at least a portion of said junctions are covered by said another insulator.

### D. "Channel Region"

# 1. Intrinsic evidence

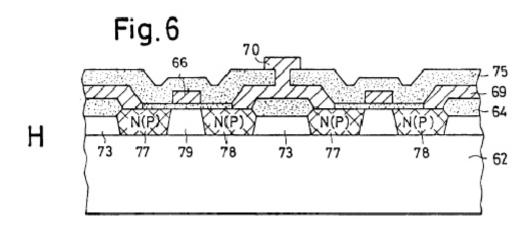

All of the asserted claims of the '463 patent require the "channel region" of the thin film transistor to have some contact with the source and drain regions. Independent claims 1, 5, 12, and 13 claim a "channel region between said source and drain region" and require the source and drain regions to "form junctions in contact" with the channel region. Independent claims 8 and 14 require only that the source and drain regions "form[] junctions" with the channel region. Figure 6H of the '463 patent specification depicts a thin film transistor:

Regions 77, 78 and 79 are the source, drain and channel regions, respectively, and all are made of a semi-amorphous semiconductor material. The specification does not discuss the differences between a one-layer channel region and a two-layer channel region.

## 2. Use of term in related patents and other extrinsic evidence

In <u>Semiconductor Energy Laboratory Co., Ltd. v. Samsung Electronics Co., Ltd.</u>, No. 96-1460-A (E.D. Va. 1998) (<u>SEL I</u>), plaintiff asserted U.S. Patent No. 5,543,636 (the '636 patent) against some of the Samsung defendants in the instant case. In <u>SEL I</u>, the defendants argued the following with respect to the '636 patent in an April 1998 claims construction brief:

SEL may argue that the majority of current path traverses along the channel in the I layer immediately adjacent the to [sic] interface between the gate insulator and the I-layer, and that this channel is both parallel to the substrate and between the source and drain regions. However, the claims require that the "source and drain regions [form] respective junctions with said channel region." Thus, the channel region cannot be limited to the portion of the bottom gate device through which charge carriers move roughly parallel to the substrate, but must also include those vertical areas through which charge carriers exit and enter the respective source and drain regions.

Dkt. #289, Exh. 2 at 24. The defendants also argued that "the channel region cannot be limited to the portion of the bottom gate device through which charge carriers move roughly parallel to the substrate, but must also include those vertical areas through which charge carriers exit and enter the respective source and drain regions." <u>Id.</u> at 23-24.

In a 2003 order construing claims in U.S. Patent No. 6,355,941 (the '941 patent), which has the same specification as the '463 patent, United States District Judge William Alsup of the Northern District of California construed "channel region" as "the area—labeled 79 of Figure 6H—between the source and drain regions through which the channel is formed; the 'channel region' includes but is not limited to the channel and does not include the insulating layer." <u>Semiconductor Energy Laboratory Co., Ltd. v. Acer Incorporated</u> (<u>Acer</u>), No. 02-02800 (N.D. Cal. June 9, 2003), dkt. #289, Exh. 1 at 9. Judge Alsup rejected one suggestion of defendants that "channel region" be construed as "the portion of the semiconductor layer through which a channel passes or in which a channel is formed." <u>Id.</u> at 8-9. The parties agreed that "channel" was the "current path between the source and drain electrodes." <u>Id.</u> at 9.

As previously noted, the '463 patent uses the term "between" to describe the location of the channel region. <u>Webster's Third New International Dictionary</u> 209 (1966) defines "between" as "from one to the other of," "in the space that separates," "JOINING, CONNECTING <a passageway—two rooms>," "in an intermediate position in relation to two other objects" and "filling the space limited by two objects."

## 3. Accused products

The thin film transistors in the accused products are manufactured by forming layers sequentially. The manufacturing process and conditions of the accused products are documented in two kinds of files. "Recipe files" specify the order in which the layers are formed and the compounds used to deposit each layer of material in the thin film transistors in the accused products. "Process flows" specify the overall manufacturing sequence, including the names of the recipe files needed to manufacture the product and the order in which the recipe files are used.

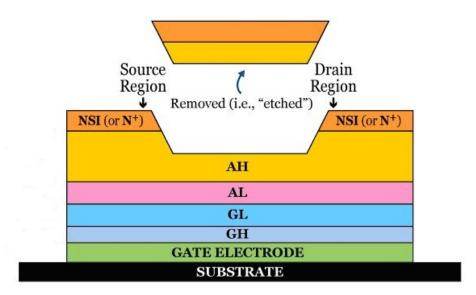

The semiconductor layers in defendants' products are formed using a process called chemical vapor deposition (CVD). One example of a chemical vapor deposition recipe used in assembling the accused products from Line 2, entitled "ACTIVE," indicates that two gate insulation layers (GH and GL) are formed on top of a gate electrode. (The parties do not indicate what the initials "GH" and "GL" refer to. The parties also fail to explain what Line 2 is; however, it appears to be a specific product production line for certain accused products.) The ACTIVE recipe provides that subsequently, three layers of semiconductor material called AL, AH and either NSI (or N<sup>+</sup>) are formed sequentially on top of the gate insulating layers. (The parties do not define what these initials stand for.)

Semiconductor materials have different "conductive properties," that is, different ways in which a current travels across the material. At the time of the alleged invention of the '463 patent, people of ordinary skill in the art used the terms "N-type," "N<sup>+</sup>-type," "P-type," "P<sup>+</sup>-type," and "I-type" to identify the conductive properties of semiconductor materials. An interface between an N-type material and an I-type material is called "NI." An interface between an N<sup>+</sup>-type material and and I-type material is called an N<sup>+</sup>I. (The parties do not agree whether the interface between an N<sup>+</sup>-type material and an I-type material can be referred to also as NI.)

| <b>NSI</b> (or <b>N</b> <sup>+</sup> ) |  |

|----------------------------------------|--|

| АН                                     |  |

| AL                                     |  |

| GL                                     |  |

| GH                                     |  |

| GATE ELECTRODE                         |  |

| SUBSTRATE                              |  |

The figure below illustrates the resulting thin film transistor in the accused products:

All of the accused products have AH and AL layers. (The parties disagree about the composition, purpose and function of the AH and AL layers.) Defendants' engineer, Seok Je Seong, testified that AL is one of the two steps that forms amorphous silicon; the other step is the AH. He stated that "two steps are what are needed to realize one amorphous layer, and this AH is — is the case where a faster deposition speed is realized on the layer." Dkt. #292, Exh. 55 at 184.

During defendants' manufacturing process, a portion of the NSI and AH layers is removed or "etched" to create separate source and drain regions in the NSI layer. The following figure illustrates this process:

The asserted '463 patent claims require the claimed source and drain regions to contain an "impurity conductivity type" (claims 1 and 12) or a "P or N type conductivity" (claims 5 and 13). The ACTIVE recipe file for Line 2 shows that the NSI layer is the only layer that contains an N-type impurity, namely phosphine (PH3). Therefore, the claimed source and drain regions of the '463 patent can be only in the NSI layer. In the accused products, the NSI layer contacts the AH layer.

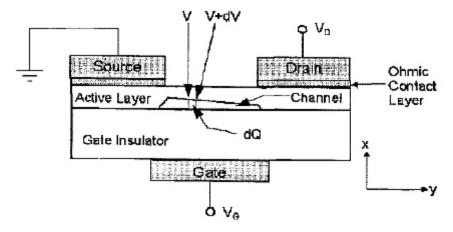

In all thin film transistors, the channel is a layer of semiconductor material along the gate insulating layer that is rendered conductive by the gate electrode. When a voltage is applied to the gate electrodes of a thin film transistor, electric charge flows from the source region through the channel region to the drain region. A conductive layer of mobile electronic charge, called the channel, forms at the interface with the gate insulating layer to

electrically connect the source and drain regions. Generally, the channel region is the region where the channel forms when the thin film transistor is on. An example of this is illustrated below:

In the accused products, when the thin film transistor is off, no current flows from the source region through either the AH or AL layer to the drain region. When the thin film transistor is turned on, current flows from the source region through the AH layer to the AL layer, then back through the AH layer on its way to the drain region.

The thickness of each layer in a thin film transistor can be determined using a technique called secondary ion mass spectrometry (SIMS), which detects the concentration of an element in a solid material. Recipe files for the accused products show that the concentration of hydrogen varies in the AL, AH and NSI (or N<sup>+</sup>) layers. The spectrometer analysis detects changes in hydrogen concentration across these layers and identifies the thickness of each layer. For example, spectrometer analysis of accused product

L2220QCFC1-TFT (from Line 2) showed that the AH layer is approximately 190 nanometers thick, the AL layer is approximately 20 nanometers thick and the NSI (or  $N^+$ ) layer is approximately 50 nanometers thick. High resolution Lorentz Electron Microscopy on this product shows a thin AL layer between the AH and GL layers. Spectrometer analysis determined that in most of the accused products, the AL layer is approximately 20 nanometers thick, and in all such cases, the AL layer is at least 10 nanometers thick.

According to an article by Andrew C. Tickle, entitled <u>Thin Film Transistors, a New</u> <u>Approach to Microelectronics</u>, "[t]ypically the channel thickness in a TFT [thin film transistor] is of the order of a few tens of Angstroms." (One nanometer equals ten Angstroms.) N. Lustig and W.E. Howard explain in "Variable Range Hopping Conductivity in Hydrogenated Amorphous Silicon Thin Film Transistors," <u>Solid State Communications</u>, Vol. 72 (1), 59-61 (1989), that the thickness of a channel in an amorphous silicon TFT "varies from about 60 [Angstroms] to about 8.5 [Angstroms] . . . ."

There are some differences in the way the AL and AH layers perform in the accused products. Process flows show that settings called "plasma power" (shown in the recipe files as "RF POWER") and "gas flow rate" (shown in the recipe files as "SIH4") are lower for the AL layer than the AH layer. Further, a test that measures the carrier mobility, which determines how easily electrons move under an applied electric field in a material, shows that the material of the AH layer has carrier mobility three times lower than that of the AL layer.

During manufacturing of the accused products, the AH layer is deposited at a much higher rate (130 nanometers in 35 seconds) than the AL layer (10 nanometers in 19 seconds).

# E. "Semiconductor Film"

#### 1. Intrinsic evidence

#### a. Claim language

Claims 8 and 14 discuss a "semiconductor film having at least source, drain and channel regions." The '463 patent specification discloses a single embodiment of a thin film transistor in which the source, drain and channel regions are formed in a single layer of semiconductor material. It also states that "a non-single crystal semiconductor layer 63 is formed to a thickness of 0.3 to 1 um on the substrate 62." The '463 patent does not disclose an embodiment in which source and drain regions are in one layer of semiconductor material. Figure 6H of the '463 patent illustrates a thin film transistor with source region 77, drain region 78, and channel region 79, all formed in a single layer of semiconductor material.

#### b. Patent prosecution

During the prosecution of the '463 patent in 1997, the patent examiner rejected pending claims of the '463 patent as obvious over the Matsumura reference in view of JP '330, Le Comber 3/79, Ovshinsky '941, and in further view of Madan 1976. The examiner

stated that "Matsumura teaches a thin film fet [field effect transistor] comprising an amorphous insulating glass substrate, an intrinsic amorphous silicon channel layer with junctions to n-type amorphous silicon source and drain regions, and a silicon dioxide gate insulating layer." Matsumura discloses a channel region located in one semiconductor layer (the "undoped I layer") and source and drain regions located in a second, separate layer above the channel layer (the "N<sup>+</sup> layer"). In Matsumura, the N<sup>+</sup> layer is located above the undoped layer. In an April 10, 1997 declaration submitted to the patent examiner, Yamazaki identified a transistor "in accordance with the present invention" that had source, drain and channel regions in a single layer of semiconductor material.

On January 14, 1999 and December 1, 1999, the examiner rejected the pending '463 patent claims again, relying this time on a number of references, including Matsumura. Nothing in the rejection letters discusses a "semiconductor film." At no point during the '463 patent prosecution did plaintiff distinguish Matsumura by claiming that the channel region was limited to channel regions on the same plane as (or co-planar with) the source and drain regions.

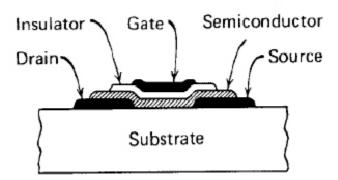

### 2. Extrinsic evidence

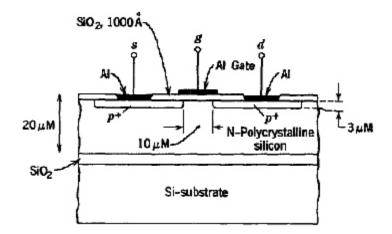

As of June 30, 1980, those of ordinary skill in the art knew of multiple designs for thin film transistors, including ones that have the source and drain in the same layer as the channel and ones that have the source and drain in a different layer from the channel. For example, the textbook <u>Theory and Applications of Field-Effect Transistors</u> (1970) by Richard S.C. Cobbold, contains the following figure, which depicts a "Weimer-Type" thin film transistor that has source and drain regions in a different layer from that containing the channel region.

(The parties do not identify which region in this figure is the "channel region.") The same textbook describes the following figure as a thin film transistor described by "Fa and Jew," which has source and drain regions labeled "p<sup>+</sup>" in the same layer as the channel region.

(The parties do not identify which region in this figure is the "channel region.")

U.S. Patent No. 5,723,371 (the '371 patent), which is assigned to Samsung Electronics Co., Ltd., explains that "[t]he typical method of fabricating a thin film transistor . . . generally comprises the steps of forming gate electrode 2 on bare glass substrate 1; depositing gate insulating film 3 on gate electrode [2]; forming semiconductor film 6 by depositing amorphous silicon film 4 and N+ amorphous silicon film 5 sequentially; and forming source and drain electrodes 7a, 7b by depositing metal layers on semiconductor film 6."

During the prosecution of the '941 patent in 1995 (which is related to the patent-insuit), plaintiff specifically proposed claims that recited "said transistor having at least source, drain, and channel regions formed within one semiconductor layer." The next year, plaintiff proposed "a pair of source and drain regions formed in the same layer as said channel region." Claim 8 of the '941 patent claims "a pair of source and drain regions formed in the same layer as said channel region."

# 3. Accused products

The accused products do not have a single layer of semiconductor material with source, drain and channel regions. The source and drain regions are in one layer and the channel region is in a different layer. (The parties dispute whether the single layer and multiple layer designs function differently. Defendants contend that a multiple layer design insures that there are no contaminants between the source, drain and channel regions and that a single layer design requires the use of ion implantation or diffusion to form source and drain regions in the same semiconductor film, a process that degrades semiconductor materials and results in lower conductivity.)

# F. "Junction"

# 1. Background

Claims 1, 5, 8 and 12-14 use the term "junctions" to refer to the border (or "interface") between two materials. An increase in voltage applied to an interface may result in a proportionate or a disproportionate increase in electric current across the interface. A current-voltage graph, also referred to as an I-V curve, shows the amount of electric current

across an interface for a given amount of voltage applied to the interface. An ohmic contact is a type of interface in which current flows across the interface in both directions with equal ease. The term "ohmic" describes a linear relationship between voltage and current; stated another way, a unit increase in voltage always results in the same increase in current flow through the junction. In an ohmic interface, an increase in voltage to the interface results in a proportional increase in electric current across the interface. Therefore, ohmic contacts produce substantially linear I-V curves.

The term "non-ohmic" describes a non-linear relationship between voltage and current: a unit increase in voltage results in a disproportionate or variable increase in current flow through the junction and produces a non-linear current-voltage graph. Non-ohmic interfaces also are referred to as "rectifying" interfaces. They allow current to flow easily in one direction. Rectifying junctions are non-ohmic. (The parties dispute whether nonrectifying junctions can be either ohmic or non-ohmic.)

NI, PI and PN interfaces are non-ohmic or rectifying. (The parties do not agree whether the  $N^+I$  interface between the source and drain regions and the channel region in the accused products is ohmic or non-ohmic. Defendants assert that these heavily doped interfaces are ohmic; plaintiff contends that they are rectifying or non-ohmic.)

## 2. Intrinsic evidence

The '463 patent refers to interfaces between the source and channel semiconductor regions as "junctions" and uses the term to describe NI, PI and PN interfaces. For example, claims 5 and 13 recite "said pair of source and drain regions . . . having a P or N type conductivity to form PI or NI junctions in contact with the channel region." Similarly, the patent specification states that "it is possible to obtain various semiconductor elements . . . . which have at least one of PI, PIN, PI [sic] and NI junctions." Col. 13, lns. 1-3. The '463 patent also refers to an ohmic contact, but in a different context:

A [sic] conductive layers 69 and 70 similar to the layer 66 extending on the insulating layer 64 are formed to make ohmic contact with the semiconductor layer 63 through the windows 67 and 68, respectively.

The specification explains that layer 66 is an "amorphous or semiamorphous semiconductor ... doped with 0.1 to 5 mol % of an N type conductive material." (The parties do not agree whether a person of ordinary skill in the art would have considered this type of material to be only  $N^+$  or also N-type. Because layer 63 does not contain any impurities, it is an I-type. Therefore, the parties also dispute whether a person of ordinary skill in the art would have understood about layers 69 and 70, that is, whether they form an  $N^+I$  ohmic contact or whether they form NI or N+I junctions with layer 66.)

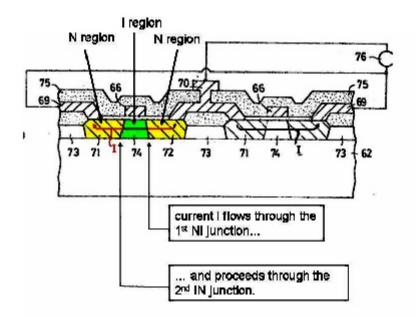

Figure 6G of the patent specification illustrates a step in the formation of an embodiment of the thin film transistor, namely the conversion of starting semiconductor

material into semi-amorphous semiconductor material through the application of a current. In Figure 6G, "current I flows through the regions 71, 72, and 74." Below is an annotated copy of Figure 6G:

The specification describes 71 and 72 as "impurity injected regions" and 73 and 74 as "nonimpurity-injected regions."

In a January 8, 1997 rejection of the pending '463 patent claims, the examiner stated that "Matsumura teaches a thin film fet [field effect transistor] comprising . . . a channel layer with junctions to n-type amorphous silicon source and drain regions. . ." A full certified translation of Matsumura indicates that the reference discloses junctions that make ohmic contact between the drain and channel regions. However, the patent examiner

considered only a partial translation of the Matsumura reference. (It is unclear from the evidence submitted by the parties whether the partial translation included the reference's use of the term "ohmic contact.")

## 3. Dictionary and textbook definitions

"Junction" has been defined generally as:

- "a region of transition between two different semiconducting regions in a semiconductor device, such as a pn junction, or between a metal and a semiconductor," <u>Dictionary of Scientific and Technical Terms</u> 1076 (1994);

- "the transition boundary between semiconductor regions of different electrical properties (for example: N-N<sup>+</sup>, P-N, P-P<sup>+</sup> semiconductors, or between a metal and a semiconductor)," <u>IEEE Standard Dictionary of</u> <u>Electrical and Electronic Terms 563 (6th ed. 1996); and</u>

- "a place where things join or meet" and "a layer or boundary which serves as the interface between semiconductor regions with different properties. For example, a *pn* junction. Also called semiconductor junction," <u>Wiley Electrical and Electronics Engineering Dictionary</u> 400 (2004).

"Junction, rectifying" is defined as "a region between two materials, typically N-type or P-type semiconductors, or between a metal and a semiconductor, arranged to provide a very low resistance to current flow in one direction and a very high resistance to current flow in the opposite direction." <u>IEEE Standard Dictionary of Electrical and Electronic Terms</u> 563.

Various references term N<sup>+</sup>I contacts ohmic contacts. "Deposition of an n<sup>+</sup> a-Si:H layer between undoped a-Si:H and a metal allows the formation of an ohmic contact between them." Cherie R. Kagan and Paul Andry, <u>Thin-Film Transistors</u> 57 (2003). "In many cases a thin n+ a-Si:H layer is sandwiched between the metal electrode and the undoped a-Si:H to make ohmic contacts." Hideharu Matsuura <u>et al.</u>, "Ohmic Contact Properties of Magnesium Evaporated Onto Undoped and P-Doped a-SI:H," <u>Japanese Journal of Applied Physics</u>, VOL. 22(3), L197-199 (Mar. 1983). "[G]ood ohmic contact was made because the i layer and the n<sup>+</sup> layer were sequentially deposited without breaking vacuum." H. Hayama and M. Matsumura, "a-SI FET IC Integrated on a Glass Substrate," <u>National Convention Record, Institute of Electrical and Comm. Engineering of Japan</u> 287-88 (Mar. 1980).

## 4. "Junction" as used in other patents

The '941 and '463 patents share the same specification and claim priority. During the prosecution of the '941 patent, plaintiff attempted to add the term "non-ohmic

junctions" to the pending claims. However, plaintiff withdrew those claims later, saying that there was an "absence of *explicit* support for this term [non-ohmic] in the specification." Dkt. #234, Exh. 102 at 15 (emphasis in original). The '941 patent has claims that recite the phrase "junctions in contact." Claim 15 of the '941 patent uses the phrase "junctions in contact" to refer to two interfaces and uses the term "ohmic contact" to refer to another interface:

a channel region extending between said source and drain regions to form junctions in contact therewith . . .

\* \* \*

an electrode in an ohmic contact with one of said source and drain regions.

In prosecuting its U.S. Patent Application No. 08/214,494 (the '494 application),

plaintiff distinguished junctions from ohmic contacts. (The '494 patent application is not

in the same family as the '463 patent.) Specifically, plaintiff distinguished U.S. Patent No.

4,766,477 (to Nakagawa), which discloses a transistor with ohmic contacts, explaining that:

Moreover, to further distinguish over Nakagawa, all claims have been amended to recite that junctions are respectively formed between the source and drain regions and the intrinsic region of the horizontal IGFET of the claims whereas in Nakagawa ohmic contacts are made between source and drains 102 and 103 and channel layer 101.

All independent claims of the related '636 patent recite the limitation "source and drain regions forming respective junctions with said channel region." In SEL I, inventor

Yamazaki testified that junctions are "quite different" from ohmic contacts. He described

an ohmic contact as having low resistance and linear characteristics. Yamazaki also stated

that "you could have a PI, an NI or a PN junction but they have non-linear characteristics."

Yamazaki Dep., Feb. 27, 1998, dkt. #210, Exh. 79 at 1386-1387 and 1389.

On February 26, 1998, plaintiff's expert in SEL I, Dr. Gerald Lucovsky, testified:

Q. And does the source region in Fig. 1 make an ohmic contact to the channel region in this structure?

A. The word ohmic contact is not an appropriate word to use for these contacts. These contacts are set up to be blocking under one set of applied potentials and to deliver and receive current under another set of those conditions. And in general, in order to make a transistor of this sort, that contact by definition is more akin to a semiconductor junction than an ohmic contact; that is, it delivers different amounts of current according to how it's driven electrically.

Lucovsky Dep., Feb. 26, 1998, dkt. #210, Exh. 78 at 121. In a later SEL I deposition taken

on April 6, 1998, Lucovsky testified that:

Q. Is the contact between the N plus source which is 107 and the amorphous silicon layer 105 which is intrinsic, an ohmic contact?

A. That contact has added, as I said before and many, many times it has added a semiconductor junction. It has a semiconductor junction because inherently and intrinsically whenever you have, a region, two regions of different conductivity type in contact with one another, there is a semiconductor junction at that interface. The current flow out of the contact can have an ohmic character if the contact can supply as much current as the material calls for.

So therefore, what I'm saying is that it would be an oversimplification and it would be an incorrect scientific statement to characterize that contact simply as ohmic because what you're doing is essentially clipping off, or if you would, taking a piece out of the context of the definition but not including the full understanding of it, and I want to make sure that we don't have any ambiguity where we don't understand what we're talking about and use words loosely.

Dkt. #292, Exh. 51 at 534-35. Later in that same deposition, Lucovsky made clear that

junction and ohmic contacts are not mutually exclusive:

Q. Have you had any tests done, or have you done any tests to determine whether the source to channel and drain to channel boundaries of any Samsung TFT are ohmic contacts?

A. Let me say it again, the source to channel and drain to channel contacts are N plus I interfaces and as Dr. Fonash, Drs. Wronski, Nikkei and every textbook teaches, there are semiconductor junctions at those contacts. Under certain conditions of the applied current and voltage that are in the operating region of a thin film transistor, those carriers supply current as needed using the Al Rose definition. Therefore those junctions act as ohmic contacts, okay? And I prefer you say the word they act as ohmic contacts, not to have a bifurcation between the word ohmic contact on the one hand and the word semiconductor junction on the other. That's wrong. That's blatantly incorrect.

Id. at 547-48. Similarly, in a March 1998 declaration in that case, Lucovsky averred:

Therefore, the '636 patent defines in a clear and unambiguous way the ni semiconductor junctions of the IGFET/TFT device structure. This definition is in complete agreement with the prevailing understanding of ni junctions as they are defined by Drs. D.E. Carlson, and C.R. Wronski in Exhibits 2 and 3, by Dr. Fonash on pages 89 and 90 of his deposition testimony.... They refer to these contacts as ohmic, which correctly describes the current flow at any particular value of gate bias voltage, but choose to ignore that there must be potential steps at the ni interface (i.e., a junction) in order for the IGFET/TFT structure to operate as a transistor device.

Lucovsky decl., Mar. 25, 1998, dkt. #292, Exh. 75, ¶ 17.

In a claim construction brief in <u>SEL I</u>, the defendants stated that "'junction,' as conventionally understood by those of skill in the art, includes 'ohmic contacts'" and agreed with Lucovsky's testimony that those of ordinary skill in the art consider "junctions" to encompass ohmic contacts. However, defendants argued that "Dr. Lucovsky's declaration is wrong as to the meaning of the term 'junction' in the Asserted Claims [of the '636 patent] because Dr. Yamazaki and SEL narrowed the meaning of that term during the prosecution history." Dkt. #289, Exh. 2 at 14. According to defendants, "[t]he prosecution history of the '636 patent reveals that, regardless of how the term junction is normally used, in the claims of the '636 patent 'junction' must be interpreted to exclude 'ohmic contacts.'" <u>Id.</u> at 12.

## 5. Accused products

A spectrometry analysis on an accused product shows that the NSI layer is a highly doped semiconductor material, which is referred to as a N<sup>+</sup>-type material. Recipe files for many of the accused products show that the AH layer does not contain any N-type or P-type impurities. The NSI and AH layer in those products form an N<sup>+</sup>I interface. At his deposition, defendants' engineer, Seok Je Seong, testified that "n<sup>+</sup> Si" is N<sup>+</sup> silicon, which is a material that "is used for the creation of ohmic contact" with the "source-drain." S.J.

Seong Dep. Vol. 2, dkt. #266 at 123. He also testified that "[o]hmic contact refers to a situation where as the pressure—correction—as the voltage is increased, commensurate with that, the current is increased as well." S.J. Seong Dep. Vol. 1, dkt. #265 at 39-40.

## F. "Non-Single Crystal Semiconductor"

### 1. Intrinsic evidence

Claims 1, 5, 12 and 13 recite source and drain regions comprising a "non-single

crystal semiconductor material." The '463 patent specification says:

The non-single crystal semiconductor 7 means a semi-amorphous semiconductor, an amorphous semiconductor or a mixture thereof and it is desired to be the semi-amorphous semiconductor. The semi-amorphous semiconductor is formed of a mixture of microcrystalline semiconductor and a non-crystalline semiconductor and the mixture is doped with a dangling bond neutralizer and the microcrystalline semiconductor has a lattice strain.

Col. 3, Ins. 37-39.

In the case where the non-single crystal semiconductor 7 is formed of the semi-amorphous semiconductor (which will hereinafter be referred to as a starting semi-amorphous semi-conductor), the region Z2 is transformed by the heat generated by the current I into the semi-amorphous semiconductor S2 which contains the microcrystalline semiconductor more richly than does the starting semi-amorphous semiconductor. Even if the non-single crystal semiconductor 7 is the amorphous semi-conductor or the mixture of the semi-amorphous and the amorphous semiconductor, the semi-amorphous semiconductor S2 is formed to have the same construction as in the case where the non-single crystal semiconductor 7 is the semi-amorphous one.

Col. 8, lns. 18-30.

The specification discusses the relative stability of the semi-amorphous semiconductor and the non-single crystal semiconductor, stating that "the semi-amorphous semiconductor S2 has stable properties as semiconductor, compared with the non-single crystal semiconductor 7." Col. 8, lns. 64-67. It also says that the "semi-amorphous semiconductor S2 assumes stable states as compared with . . . the amorphous semiconductor . . . ." Col. 9, lns. 48-50.

The specification explains that the semi-amorphous material provides "excellent properties" as a semiconductor device, col. 9, lns. 56-67, and adds that

The non-single crystal region S1 does not possess the above said excellent properties of the semi-amorphous semiconductor region S2. Especially, the region S1 does not have the excellent conductivity characteristic of the region S2 and the former can be regarded as an insulating region relative to the latter. Consequently, the non-single crystal semiconductor region S1 electrically isolates the semi-amorphous semiconductor regions S2 from adjacent ones of them.

Col. 9, Ins. 62-67; Col. 10, Ins. 1-3. The specification explains that to manufacture source,

drain and channel regions, amorphous semiconductor material is heated and "undergoe[s]

a structural change into semi-amorphous semiconductor" material, which makes up the

source, drain, and channel regions:

Next, a description will be given, with reference to FIGS. 6A to 6H, of a second embodiment of the semiconductor device of the present invention, together with its manufacturing method.

\* \* \*

... the regions 71, 72 and 74 respectively undergo a structural change into semi-amorphous semiconductor regions 77, 78 and 79, respectively, as shown in FIG. 6H.

In this way, the semiconductor device of the second embodiment of the present invention is obtained.

Col. 10, lns. 34-37 and col. 11, lns. 18-29.

In the semiconductor device of the present invention shown in FIG. 6H, the regions 77, 78 and 79 correspond to the semi-amorphous semiconductor region S2 in FIG. 1G, providing excellent properties as a semiconductor device. The region 73 corresponds to the non-single crystal semi-conductor S1 in FIG. 1G, and hence it has the property of an insulator. The regions 77, 78 and 79 are encompassed by the region 73, so that the regions 77 to 79 are essentially isolated from the other adjoining regions 77 to 79 electrically.

Col. 11, Ins. 30-38.

Moreover, the semi-amorphous semiconductor forming the semiconductor device of the present invention permits direct transition of electrons even at lower temperatures than does the amorphous semiconductor.

Col. 12, Ins. 62-65.

#### 2. Extrinsic evidence

One textbook states that "[s]ingle-crystal materials have more uniform and predictable properties than polycrystalline materials." Peter Van Zant, <u>Microchip</u> Fabrication 51 (3d ed. 1997).

In a June 9, 2003 claim construction order in <u>Acer</u>, Judge Alsup determined that "non-single crystal semiconductor material" as used in the '941 patent should be construed as it is defined in the specification, which is the same specification used in the '463 patent.

Regardless whether an amorphous or semi-amorphous semiconductor is used, using silicon nitride instead of silicon oxide in the gate insulator provides a thin film transistor with better resistance to degradation while still insulating the channel region from the gate electrode of the thin film transistor.

## G. "Intrinsic" Amorphous Semiconductor Material

Claims 5 and 13 state that the channel region comprises "an intrinsic amorphous silicon semiconductor material doped with a recombination center neutralizer selected from the group consisting of H, a halogen and a combination thereof." These claims also recite "said pair of source and drain regions . . . having a P or N type conductivity to form PI or NI junctions in contact with said channel region."

The '941 patent also recites the claim limitation of an "intrinsic" semiconductor material. On February 27, 1998, Yamazaki testified as follows with respect to the '941 patent at issue in SEL I:

Q. Then it goes on to say "We should seek Dr. Yamazaki's further comments on the particular advantages of the intrinsic semiconductor in this

context for use in the interview presentation." Dr. Yamazaki, my question to you is are there other advantages that you're aware of?

A. The general meaning of I type is one in which there are as few impurities as possible. Therefore, if you put in P or N type impurities deliberately, or if oxygen which results in N type characteristic gets in, then the characteristics deteriorate.

Dkt. #210, Exh. 79 at 1448. In Acer, plaintiff's proposed construction of "intrinsic" was

"not intentionally doped with an efficient dopant." However, the court found that the

proposed construction invited "controversy as to what counts as an efficient dopant." In the

final claim construction order, Judge Aslup wrote:

## At this juncture, this order holds that "intrinsic" refers to pure or near pure semiconductor material that has not previously been doped....

To the extent any further construction is required, it will await additional expert testimony regarding the meaning of intrinsic as applied to amorphous or semi-amorphous semiconductor materials.

Dkt. #290, Exh. 288 at 7 (emphasis in original). The '463 patent cites the final claim

construction order in <u>Acer</u> as a reference.

### H. Sakamoto Reference

Japanese Patent Publication No. 55-19820 ("Sakamoto"), entitled "Semiconductor

Device," was filed on July 27, 1978 and published on February 12, 1980, before the '463

patent's claimed priority date of June 30, 1980. However, plaintiff did not provide the

Sakamoto publication to the U.S. Patent and Trade Office during the prosecution of the '463 patent. Sakamoto discloses semiconductor devices that may be used in integrated circuit memory.

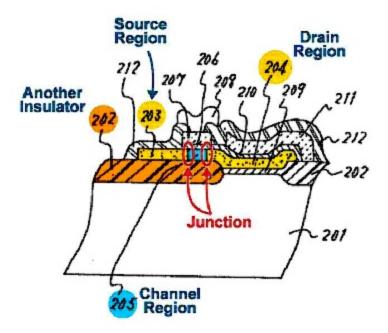

Sakamoto teaches two embodiments of a thin film transistor. The second embodiment is depicted in Figure 2 below. (The regions marked 202, 203, 204 and 205 have been shaded and labeled by defendants in this version of Figure 2.)

The second embodiment of Satamoto discloses all of the elements of the asserted '463 patent claims except for (1) an amorphous source, drain and channel region doped with a "recombination center neutralizer, such as hydrogen, a halogen, or a combination thereof" and (2) an "intrinsic channel region." Although Sakamoto states that the source and drain regions contain "effective dopants," it does not define that term. Figure 2 shows dots in the

source and drain regions, labeled as 203 and 204, without any explanation of the meaning of the dots. The channel region in Figure 2 does not contain any dots.

In the second embodiment, Sakamoto also sets forth the following steps for constructing a Metal Oxide Semiconductor (MOS) field-effect transistor, which is a thin film transistor:

In the MOS field-effect transistor for the cell unit, either the first polysilicon or amorphous silicon film 203 or 204 that is formed on the thick silicon oxide film containing effective dopants is used as a source or drain, respectively; and similarly, a part of the surface of the either polysilicon or amorphous silicon film 205 is used as a channel region; and the thin insulator 206 (for example, a silicon nitride film), the second polysilicon or amorphous silicon film 207 containing dopants, and the metallic electrode 208 are used as the gate film, the gate electrode, and the word line in the MOS field-effect transistor, respectively.

Dkt. #208, Exh. 6 at 3. Sakamoto explains that the channel is formed in "a part of the surface of . . . amorphous silicon film 205." <u>Id.</u> The amorphous silicon thin film transistor that Sakamoto discloses has source and drain regions doped with N-type or P-type impurities.

### I. Amorphous Silicon and Recombination Centers

Amorphous silicon is cheaper to fabricate than single crystal or polycrystalline silicon.

It can be made at low temperatures, allowing the use of "cheaper" material (such as glass substrates instead of quartz or silicon) on which to build devices. Amorphous silicon can be formed by the processes of evaporation or sputtering. However, as explained in plaintiff's Japanese Patent Application No. 55-88974 (JP '974), to which the '463 patent claims priority:

Because it is random in all aspects, the amorphous semiconductor is not necessarily stable in terms of free energy as compared with crystalline semiconductor . . . and, owing to its random property, there exist in the amorphous semiconductor a large number of dangling bonds which are no[t] chemically bonded with each other. The dangling bonds serve as recombination centers which extremely reduce the carrier life.

The parties agree that, in other words, dangling bonds in amorphous silicon act as recombination centers that can trap charged particles (charge "carriers").

Amorphous silicon formed by evaporation or sputtering does not include a recombination center neutralizer unless one is added by a process called doping. When Sakamoto was filed in 1978, it was known that dangling bonds in amorphous silicon could be neutralized by doping the material with hydrogen or a halogen. (Halogen refers to a group of highly reactive elements including fluorine, chlorine, bromine, iodine and astatine.) Amorphous silicon doped with hydrogen (a-Si:H) as a recombination center neutralizer is referred to as "hydrogenated amorphous silicon."

According to R.A. Street, <u>Hydrogenated Amorphous Silicon</u> 1 (Cambridge University Press 1991), hydrogenated silicon was first made in the late 1960s. Before that time, research on amorphous silicon without hydrogen showed that it has a "very high defect density, which prevents doping, photoconductivity and other desirable characteristics of a useful semiconductor." <u>Id.</u> Street explains that it was discovered later that amorphous silicon could be made from silane gas (SiH<sub>4</sub>) by a technique called glow discharge:

The essential role of the hydrogen in a-Si:H was first recognized . . . at Harvard . . . . They understood that the high defect density of amorphous silicon . . . prevented [it] from being useful for electronic devices and tried to find ways of eliminating the defects, eventually succeeding by introducing hydrogen into the sputtering system. The hydrogen caused a similar improvement in the material properties as was found for glow discharge a-Si:H, with a high photoconductivity, low defect density and doping. . . . Shortly after the Harvard experiments, it was confirmed that the glow discharge material also contained hydrogen. . . . This is now recognized as an essential component of the films which is responsible for suppressing defects.

<u>Id.</u> at 2. "A major turning point in the development of a-Si:H was the report in 1975 of substitutional n-type or p-type doping by the addition of phosphine or diborane to the deposition gas (Spear and LeComber 1975)." <u>Id.</u> SiH<sub>4</sub> has "good electrical transport properties with a fairly high carrier mobility . . . and also strong photoconductivity resulting from a very low defect density . . . ." <u>Id.</u> at 1.

Using hydrogen or a halogen as a recombination center neutralizer was known and accepted by at least some academics prior to the alleged invention of the '463 patent. By the time the '463 patent was filed (priority date of June 30, 1980), glow discharge decomposition of silane was a known technique in the art. Also at this time, it was known that amorphous silicon could be deposited through a technique known as glow discharge

decomposition of silicon tetrafluoride  $(SiF_4)$  to produce amorphous silicon doped with fluorine (a halogen). Doping amorphous silicon with hydrogen as a dangling bond neutralizer is admitted prior art in the '463 patent file history.

Transistors constructed from pure amorphous silicon are less effective than those constructed from doped amorphous silicon. Silicon has an important advantage over other semiconductor materials because its conductivity can be improved by the addition of N-type or P-type impurities. Doping amorphous silicon with N-type or P-type impurities allows the source and drain regions to form in a single layer of amorphous silicon semiconductor material. U.S. Patent No. 4,217,374 (Ovshinsky '374), which was filed on March 8, 1978, states:

Accordingly, a considerable effort has been made to develop processes for readily depositing amorphous semiconductor films, each of which can encompass relatively large areas, if desired, limited only by the size of the deposition equipment, and which could be readily doped to form p and n junctions where p-n junction devices are to be made therefrom equivalent to those produced by their crystalline counterparts. For many years such work was substantially unproductive. Amorphous silicon or germanium (Group IV) films were found to have microvoids and dangling bonds and other defects which produce a high density of localized states in the energy gap thereof. The presence of a high density of localized states in the energy gap of amorphous silicon semiconductor films results in a low degree of photoconductivity and short diffusion lengths, making such films unsuitable for solar cell applications. Additionally, such films cannot be successfully doped or otherwise modified to shift the Fermi level close to the conduction or valence bands, making them unsuitable for making p-n junctions for solar cell and current control device applications.

U.S. Patent No. 4,226,898 (Ovshinsky '898), which was filed on March 16, 1978, contains a similar statement.

### J. "Recombination Center Neutralizers" in other Prior Art

Before the June 1980 priority date of the '463 patent, a number of publications disclosed the use of *hydrogen* as a recombination center neutralizer in amorphous silicon: W.E. Spear and P.G. LeComber, "Investigation of the Localised State Distribution In Amorphous Si Films," Journal of Non-Crystalline Solids (1972); A. Madan, Electronic Transport and State Distributions in Amorphous Silicon Films 29 (1973); M. Hirose et al., "Electronic Density of States in Discharge-produced Amorphous Silicon," <u>Applied Physics Letters</u> 34:3, p. 1 (1979); H. Hayama and M. Matsumura, <u>Amorphous Silicon Thin-Film MOS Transistors, Transactions of the Institute of Electrical and Communication Engineering of Japan J63-2</u> (Feb. 1980); and H. Hayama, "Amorphous Silicon Thin-film Metal-Oxide-Semiconductor Transistors," <u>Applied Physics Letters</u> (May 1980).

Before June 1980, the following publications disclosed the use of *either a halogen or hydrogen* as a recombination center neutralizer in amorphous silicon: JP '974; U.S. Patent No. 4,217,374 (Ovshinsky '374) (filed Mar. 8, 1978); W.E. Spear, "Introductory Talk: Localized States In Amorphous Semiconductors," <u>Proc. Fifth International Conference on</u> Amorphous and Liquid Semiconductors 6 (1974); A. Madan et al., "Investigation of the Density of Localized States in a-Si using the Field Effect Technique," <u>Journal of</u> <u>Non-Crystalline Solids</u> 20, 239-57 (1975); A.K. Malhotra and G.W. Neudeck, "Effects of Hydrogen Contamination on the Localized States in Amorphous Silicon," <u>Applied Physics</u> (1976); and P.G. Le Comber <u>et al.</u>, "Amorphous-silicon Field-effect Device and Possible Application," <u>Electronics Letters</u> (1979). (The parties dispute whether the following references disclose the use of hydrogen or a halogen as a recombination center neutralizer for amorphous silicon: U.S. Patent No. 4,226,898 (Ovshinsky '898) (filed Mar. 16, 1978); JP 55-50663 (published Apr. 12, 1980); and JP 55-50664 (published Apr. 12, 1980); H. Hayama and M. Matsumura, "a-Si FET IC Integrated On A Glass Substrate," <u>National</u> <u>Convention Record, Institute of Electrical and Communication Engineering of Japan</u> 287-88 (Mar. 1980)).

(Although plaintiff cites several references that allegedly disclose thin film transistors composed of amorphous silicon without a recombination center neutralizer, it has not proposed a finding of fact to that effect. Instead, it cites the references only in its briefs or in response to defendants' proposed findings of fact. Therefore, I have not considered those references.)

During prosecution of the '463 patent, the examiner rejected the pending claims in light of U.S. Patent No. 4,485,389 (Ovshinsky '389), which identifies "current control

devices" as including "transistors" and explains that fluorine can be used as a recombination

center neutralizer. Also during prosecution of the '463 patent, plaintiff stated in 1991 that

Typically with amorphous semiconductor materials, the dangling bond neutralizer doping level may be as high as 25 to 30 mol% in order to insure termination of all of the dangling bonds present in such amorphous material. However, due to the presence of crystalline structures in semi-amorphous semiconductor material, there are less dangling bonds and therefore less dangling bond neutralizer can be utilized to terminate the dangling bonds.

Dkt. #303, Exh. 508 at 4-5. Later, during the '463 patent prosecution in 1994, plaintiff

stated that

[A]lthough hydrogen as a dangling bond neutralizer in general for <u>amorphous</u> materials, for example, was known as evidenced by column 3 of Ovshinsky's discussion of the prior art, the fact remains that there is no recognition or suggestion whatsoever in Oshinsky to use hydrogen alone in the 1-5% range.

Applicant acknowledges that hydrogen alone was known as a dangling bond neutralizer for amorphous semiconductor materials. In fact, as discussed at column 6, lines 49-68 of U.S. Patent 4,409,134, of record, to the applicant S. Yamazaki, 20-30% of hydrogen is necessary to terminate the numerous dangling bonds that exist in amorphous semiconductor material. However, with the SAS material of the present invention, there are less dangling bonds to be terminated and thus hydrogen alone can be used in an amount less than 5 mol%, as recognized by the applicant S. Yamazaki, for SAS material.

Dkt. #208, Exh. 14 at 7.

K. Matsumura Reference

In March 1980, Drs. Hiroshi Hayama and Masakiyo Matsumura of the Tokyo Institute of Technology published a paper titled "a-Si FET IC Integrated on a Glass Substrate" (Matsumura). (The reference is prior art to the '463 patent and was cited by the patent examiner during the '463 patent prosecution.) Matsumura discloses an amorphous silicon thin film transistor with all the elements of the asserted '463 patent claims except a silicon nitride gate insulating film.

## L. LeComber

P.G. LeComber, "Amorphous Silicon Field Effect Device and Possible Applications," <u>Electronics Letters</u>, V. 15, No. 6 (Mar. 15, 1979) is prior art to the '463 patent and was considered by the patent office during the prosecution of the '463 patent. Like Matsumura, LeComber focuses on amorphous silicon thin film transistors. LeComber discloses a thin film transistor designed for use in an LCD panel, specifically an insulated-gate field-effect transistor made of amorphous silicon deposited by a glow discharge technique. One embodiment disclosed in the reference shows two thin film transistors with source, drain and gate electrodes. The channel region disclosed in LeComber consists of amorphous silicon and the gate insulator consists of silicon nitride.

### M. Gate Insulators

Although the composition of the gate insulators disclosed in Matsumura (silicon oxide) and LeComber (silicon nitride) differ, both types of gate insulators serve the same function of insulating the gate electrode from the channel region, which allows the transistors to switch on and off. Matsumura and LeComber were well known to those of ordinary skill in the art in the late 1970s. Further, a person of ordinary skill in the art likely would have known that Matsumura had cited the work of LeComber in certain papers. For example, Matsumura and Hayama published an article entitled "Amorphous-Silicon Thin-Film Metal-Oxide-Semiconductor Transistors" in <u>Applied Physics Letters</u>, Vol. 26, No. 9, on May 1, 1980, in which they cited LeComber on gate insulators.

At the time of the alleged invention of the '463 patent (June 1980), it was well known that a crystalline transistor with silicon nitride provided better protection against harmful charged particles than one with silicon oxide and was more resistant to radiation exposure. Following the filing of the '463 patent, people of skill in the art continued to analyze the use of silicon nitride insulators in amorphous silicon thin film transistors. For example, an article published by M.J. Powell in 1985 compared silicon oxide and silicon nitride gate insulators and noted advantages and disadvantages to both. A 1989 paper by Powell described further investigations of the differences between these insulators and concluded that nitride is superior to oxide in amorphous thin film transistors.

#### N. Matsumura and LeComber in SEL I

In <u>SEL I</u>, plaintiff brought claims that defendants' LCD products infringed U.S. Patent 5,543,636 (the '636 patent). The U.S. District Court for the Eastern District of Virginia found the '636 patent unenforceable for inequitable conduct in part because plaintiff disclosed to the patent office only a partial translation of Japanese Application No. 56-135968 (Canon), which discloses the combination of an amorphous silicon thin film transistor with a silicon nitride gate insulator.

In a subsequent motion for reconsideration, plaintiff argued that the court erred in finding that Canon was not cumulative of other information before the patent office, including Matsumura and LeComber. In support of its argument, plaintiff filed a declaration by Dr. Masakiyo Matsumura, who averred that Figure 1 in his reference shows, among other things, an undoped or intrinsic amorphous silicon semiconductor layer, an  $n^+$  or doped source and drain with aluminum electrodes and a silicon oxide (SiO<sub>2</sub>) gate insulator. He averred that the channel region is formed in the undoped or intrinsic amorphous silicon semiconductor layer between the  $n^+$  source and drain. Matsumura also averred that the amorphous silicon of the source, drain and channel regions was deposited by "glow discharge" or the decomposition of silane.

Also in support of its motion for reconsideration of the inequitable conduct ruling, plaintiff submitted a claim chart showing that the following claim limitations in the '636

patent were disclosed by Matsumura: (a) a "TFT" or thin film transistor; (b) "Intrinsic Amorphous Silicon Semiconductor layer with [a] Channel Region;" and (c) a channel region "Sandwiched between [a] Gate Insulator and Another Insulator." The chart also shows that as compared to Canon, Matsumura is missing the limitations of a "Silicon nitride gate Insulator" and the concentration limits on carbon (C), nitrogen (N) and oxygen (O) in the channel region. Plaintiff admitted in its motion for reconsideration that Matsumura disclosed the co-planar thin film transistor structure from the '636 patent with the exception of its silicon nitride gate insulator:

Fig. 1 [of Matsumura] . . . discloses a coplanar TFT with the same intrinsic amorphous silicon sandwiching structure found in the '636 patent. The only difference in structure is the gate insulator. In Matsumura, the gate insulator is made of silicon oxide rather than silicon nitride.

In his declaration, Dr. Matsumura averred that he knew from a paper by P.G. LeComber, entitled "Amorphous Silicon Field Effect Device and Possible Applications," that silicon oxide can be replaced by silicon nitride as the gate insulator.

In its motion for reconsideration, plaintiff stated the following:

The combination of silicon nitride with the intrinsic amorphous silicon sandwiching structure in Matsumura, however, is suggested by other information before the [US]PTO.

\* \* \*

[I]n a . . . Information Disclosure Statement filed with the Patent Office . . ., the use of silicon nitride as a gate insulator was spelled out from [sic] the

Examiner several times, including in connection with the discussion of Matsumura's intrinsic amorphous silicon sandwich structure. The pertinent portions from . . . the IDS state the following:

[T]he following Japanese Patents disclose the use of silicon nitride for a gate insulating layer of a thin film transistor: 56-135968, 55-50663 and 55-50664.

\* \* \*

The Examiner's attention is particularly directed to Reference (18) to LeComber et al. which appears to disclose the use of a silicon nitride layer as a gate insulator.

\* \* \*

Reference (12) to Matsumura teaches a TFT having a non-doped i-type amorphous silicon film formed on a glass substrate, n + layers as source and drain regions formed on the i-type silicon film and a silicon oxide (SiO<sub>2</sub>) layer as a gate insulating layer.

Thus, having a single reference showing silicon nitride in combination with the intrinsic amorphous silicon sandwiching structure is not material, given that the combination is clearly taught by other information before the PTO. As noted above, this other information informed the Examiner of the prior art use of silicon nitride as a gate insulator and its known interchangeability with silicon oxide.

Dkt. #209, Exh. 35 at 12-13.

### O. Matsumura and LeComber in the '463 Patent Prosecution

During the prosecution of the '463 patent, the examiner rejected the application several times before issuing a final rejection of the claims as obvious over Matsumura in view of LeComber, Yamazaki '330, Ovshinski '941, Madan, and Yamazaki '663. (Although the parties do not say so, I assume that the "Yamazaki" named in these references refers to the named inventor on the '463 patent.) Plaintiff appealed the examiner's final rejection to the Board of Patent Appeals and Interferences, arguing that it would not be obvious to combine Matsumura and LeComber because they disclosed different types of transistors:

Also, with respect to LeComber, it is important to note that the type of transistor disclosed by LeComber is entirely different from the transistor disclosed by Matsumura. That is, while the transistor disclosed by Matsumura has junctions between two semiconductor materials having different conductivity type, the transistor of LeComber utilizes Schottky junction, that is, a semiconductor-oxide-metal junction. As noted above, unique problems (that are clearly not disclosed or suggested by the prior at [sic]) result in a device having such junctions, which are not present in the device of LeComber.

In a November 30, 1999 answer to the appeal, the patent examiner explained that using halogen to reduce dangling bonds in amorphous semiconductor material was "fundamentally obvious from the teachings of Yamazaki '330 and Ovshinsky '941." Dkt. #224, Exh. 264 at 4-5. "Both Yamazaki and Ovshinsky recognized the advantages of including hydrogen or halogen . . . in amorphous semiconductor material to improve device function." <u>Id.</u> The examiner also noted that nitride had been disclosed as a gate insulating film in the prior art and stated that

Both silicon oxide and silicon nitride gate insulating films in field effect transistor devices were well known at the time of applicant's invention and there is clearly a preponderance of evidence that their practice in thin film transistor devices was not and would not have been unobvious.

<u>Id.</u> at 5-6.

On May 27, 2004, the Board of Patent Appeals and Interferences allowed the claims of the '463 patent to issue over the considered references. In reversing the patent examiner's rejection, the board noted that the examiner relied on LeComber and Madan for a gate insulating film comprising a nitride and on Matsumura for the general teaching related to the claimed source, drain and channel regions, even though Matsumura does not teach silicon oxide gate insulating films. It found that the examiner had not "provided a convincing rationale as to why Le Comber, taken with Matsumura, would have rendered obvious the proposed modifications." Dkt. #224, Exh. 265 at 5. The board determined that "LeComber would not have been considered by the artisan as applicable to the type of device disclosed by Matsumura, and thus would not have suggested modification of the device. . . [T]he references disclose different structures, and LeComber does not discuss the reference's teachings as applied to other environments." Id. The board found "no suggestion that the silicon nitride film used in the IGFET [i.e., "insulated gate field effect transistor"] is also recommended, or even suitable, for a device having the type of junctions in the Matsumura device." Id.

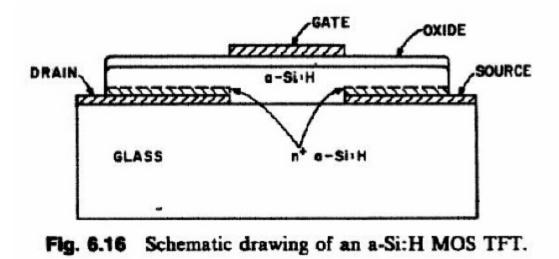

### P. Kazmerski Reference

<u>Polycrystalline and Amorphous Thin Films and Devices</u> is a book edited and published by Lawrence L. Kazmerski in 1980 as part of the "Materials Science Series." Chapter 6 of the book is entitled "Amorphous Thin-Film Devices" and section 6.4.6 is entitled "Thin-Film Transistors." Figure 6.16 of this reference depicts a silicon oxide gate insulating film (labeled "OXIDE") arranged between a gate electrode and an a-Si:H film:

On the same page that Figure 6.16 appears in the reference, Kazmerski states:

Spear and LeComber [75] used a similar field-effect type of device to determine the density of states in a-Si:H. However, in that early work, a glass substrate (~250 *J*-tm thick) was used as the insulating layer between the gate electrode and the a-Si:H. Thus gate voltages as large as 1 kV had to be applied to modulate the drain current by a factor of  $10^3$ . In later work by Madan et al. [46] a thin film of amorphous Si<sub>3</sub>N<sub>4</sub> (~1-3 *J*-tm thick) was used as the

insulating layer, and then gate voltages of ~ 50 V were able to produce a modulation of ~  $10^3$  in the drain current.