## Exhibit 28

| Office Action in Ex Parte Reexamination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                          | Control No.<br>90/011,311 | Patent Under Reexamination |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------|----------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                           | 5,915,131                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          | Examiner Woo H. Choi      | Art Unit<br>3992           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                           | 0332                       |  |  |

| The MAILING DATE of this communication appears on the cover sheet with the correspondence address                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                          |                           |                            |  |  |

| a Responsive to the communication(s) filed on <u>01 November 2010</u> b This action is made FINAL.  c A statement under 37 CFR 1.530 has not been received from the patent owner.                                                                                                                                                                                                                                                                                                                                                                      |                                                                                          |                           |                            |  |  |

| A shortened statutory period for response to this action is set to expire 2 month(s) from the mailing date of this letter.  Fallure to respond within the period for response will result in termination of the proceeding and issuance of an ex parte reexamination certificate in accordance with this action. 37 CFR 1.550(d). EXTENSIONS OF TIME ARE GOVERNED BY 37 CFR 1.550(c). If the period for response specified above is less than thirty (30) days, a response within the statutory minimum of thirty (30) days will be considered timely. |                                                                                          |                           |                            |  |  |

| Part I THE FOLLOWING ATTACHMENT(S) ARE PART OF THIS ACTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                          |                           |                            |  |  |

| 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ☐ Notice of References Cited by Examiner, PTO-89                                         | 2. 3. Interview Summa     | ry, PTO-474.               |  |  |

| 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ☐ Information Disclosure Statement, PTO/SB/08.                                           | 4.                        |                            |  |  |

| Part II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Part II SUMMARY OF ACTION                                                                |                           |                            |  |  |

| 1a.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ☐ Claims <u>1-20</u> are subject to reexamination.                                       |                           |                            |  |  |

| 1b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Claims are not subject to reexamination.                                                 |                           |                            |  |  |

| 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2. Claims have been canceled in the present reexamination proceeding.                    |                           |                            |  |  |

| 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Claims 11 and 14 are patentable and/or confirmed.                                        |                           |                            |  |  |

| 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ☑ Claims <u>1-10,12,13 and 15-20</u> are rejected.                                       |                           |                            |  |  |

| 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Claims are objected to.                                                                  |                           |                            |  |  |

| 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | The drawings, filed on are acceptable.                                                   |                           |                            |  |  |

| 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ☐ The proposed drawing correction, filed on has been (7a) ☐ approved (7b) ☐ disapproved. |                           |                            |  |  |

| 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8. Acknowledgment is made of the priority claim under 35 U.S.C. § 119(a)-(d) or (f).     |                           |                            |  |  |

| a) ☐ All b) ☐ Some* c) ☐ None of the certified copies have                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                          |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 been received.                                                                         |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 not been received.                                                                     |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3 been filed in Application No                                                           |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4 been filed in reexamination Control No                                                 |                           |                            |  |  |

| 5 been received by the International Bureau in PCT application No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                          |                           |                            |  |  |

| * See the attached detailed Office action for a list of the certified copies not received.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                          |                           |                            |  |  |

| 9. Since the proceeding appears to be in condition for issuance of an <i>ex parte</i> reexamination certificate except for formal matters, prosecution as to the merits is closed in accordance with the practice under <i>Ex parte</i> Quayle, 1935 C.D. 11, 453 O.G. 213.                                                                                                                                                                                                                                                                            |                                                                                          |                           |                            |  |  |

| 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Other:                                                                                   |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                           |                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                           |                            |  |  |

Application/Control Number: 90/011,311

Art Unit: 3992

.

#### **DETAILED ACTION**

#### Reexamination

- 1. This is an *ex parte* reexamination of U.S. Patent Number 5,915,131 ('131 patent) requested by a third party requester. Claims 1-20 are subject to reexamination. The references discussed herein are as follows:

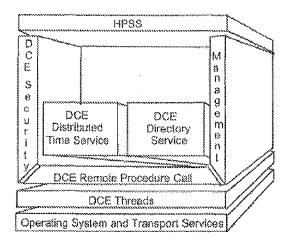

- Teaff, Danny, et. al, "The Architecture of High Performance Storage Systems (HPSS)," 4<sup>th</sup> NASA Goddard Conference on Mass Storage Systems and Technologies, March 29-30, 1995 ("Teaff");

- 2. U.S. Patent No. 5,566,346 ("Andert").

### Claim Rejections - 35 USC § 102

2. The following is a quotation of the appropriate paragraphs of 35 U.S.C. 102 that form the basis for the rejections under this section made in this Office action:

A person shall be entitled to a patent unless -

(e) the invention was described in (1) an application for patent, published under section 122(b), by another filed in the United States before the invention by the applicant for patent or (2) a patent granted on an application for patent by another filed in the United States before the invention by the applicant for patent, except that an international application filed under the treaty defined in section 351(a) shall have the effects for purposes of this subsection of an application filed in the United States only if the international application designated the United States and was published under Article 21(2) of such treaty in the English language.

- 3. Claims 1-6 are rejected under 35 U.S.C. 102(a) as being anticipated by Teaff.

- With respect to claim 1, Teaff discloses a computer system (p. 3, Figure 1) comprising:

a bus (Figure 1, control buses that connect network elements and workstations to the

HPSS servers; also, a bus is an inherent component of a computer system);

Page 2

Art Unit: 3992

at least one memory (Figure 1, network attached memories or other memories in servers and workstations) coupled to the bus for storing data and programming instructions that include applications and an operating system; and

a processing unit (Figure 1, servers and workstations) coupled to the bus and running the operating system and applications by executing programming instructions (see pp. 4-5, Modularity and APIs, and Portability and Standards), wherein an application has a first plurality of tailored distinct programming interfaces (p. 4, "The HPSS software components are loosely coupled, with open application program interfaces (APIs) defined at each component level"; see also Appendix A for a list of tailored APIs) available to access a plurality of separate sets of computer system services (p. 4, "Most users will access HPSS at its high level interfaces – client API, FTP, (both parallel and sequential), NFS, Parallel File system (PFS), with AFS/DFS, ...") through the operating system of the computer system via service requests (see Figures 2 and 3, and the text associated with the figures; see Figure 6 for an example of security service requests handled through the operating system).

5. With respect to claim 3, see the discussion of claim 1 above. Teaff discloses that the operating system comprises a plurality of servers (see Figures 1 and 2, HPSS Servers, name servers, location servers, etc.; see also Appendix A), and each of the first plurality of programming interfaces transfer service requests to one of the plurality of servers, wherein each of the plurality of servers responds to service requests from clients of the separate sets of I/O services (see p. 4, Modularity and APIs and Figure 2; Appendix A).

Art Unit: 3992

- 6. With respect to claim 2, each of the first plurality of tailored distinct programming interfaces are tailored to a type of I/O service provided by each set of I/O services (p. 4, Modularity and APIs; see also Appendix A, APIs are tailored for each type of services).

- 7. With respect to claim 4, service requests are transferred as messages in a messaging system (p. 8, "HPSS uses the DCE Remote Procedure Call (RPC) mechanism for control messages and DCE Threads for multitasking").

- 8. With respect to claim 5, each of the plurality of servers supports a message port (see p. 10, Communication, "The control path communication between HPSS components is through DCE RCPs or Encima transaction RPCs. For data path communication, the HPSS Mover(s) currently utilize either Sockets or IPI-3 (over HIPPI) libraries.").

- 9. With respect to claim 6, at least one of the plurality of servers is responsive to service requests from applications and from at least one other set of I/O services (see p. 14, Physical Volume Library, "The volume mount service is provided to clients such as a Storage Server").

- 10. Claims 1-10, 12-13, and 15-20 are rejected under 35 U.S.C. 102(a) as being anticipated by Andert.

- With respect to claim 1, Andert discloses a computer system (Figure 10) comprising: a bus (see Figures 4, 7, and 8);

Application/Control Number: 90/011,311

Art Unit: 3992

Page 5

at least one memory (Figure 10, 1008) coupled to the bus for storing data and programming instructions that include applications and an operating system; and

a processing unit (1006) coupled to the bus and running the operating system (1014) and applications (1030) by executing programming instructions, wherein an application has a first plurality of tailored distinct programming interfaces (see Figure 1 and c8:30-44) available to access a plurality of separate sets of computer system services (c8:45-67) through the operating system (see Figure 5, applications 1030 access I/O services provided by Device Ensembles 1032 through the operating system 1014; see also c3:47-49) of the computer system via service requests (c1:59-62).

- 12. With respect to claim 3, see the discussion of claim 1 above. Andert discloses that the operating system comprises a plurality of servers (see Figures 1 and 2, IO services frameworks), and each of the first plurality of programming interfaces transfer service requests to one of the plurality of servers, wherein each of the plurality of servers responds to service requests from clients of the separate sets of I/O services (see Figure 1, c10:1-6).

- 13. With respect to claim 2, each of the first plurality of tailored distinct programming interfaces are tailored to a type of I/O service provided by each set of I/O services (see Figure 1; see also c8:45-67).

- 14. With respect to claim 4, service requests are transferred as messages in a messaging system (c10:1-6 and c17:36-40).

Art Unit: 3992

- 15. With respect to claim 5, each of the plurality of servers supports a message port (see c17:36-53, the message port limitation reads on the means for receiving messages from application programs and interrupt service means).

- 16. With respect to claim 6, at least one of the plurality of servers is responsive to service requests from applications and from at least one other set of I/O services (c9:1-11).

- 17. With respect to claim 7, the operating system further comprises a plurality of activation models, wherein each of the plurality of activation models is associated with one of the plurality of servers to provide a runtime environment for the set of I/O services to which access is provided by said one of the plurality of servers (c11:25-58).

- 18. With respect to claim 8, at least one instance of a service is called by one of the plurality of servers for execution in an environment set forth by one of the plurality of activation models (c11:25-58).

- 19. With respect to claim 9, Andert discloses a computer system comprising:

a bus (see claim 1 above);

- at least one memory coupled to the bus for storing data and programming instructions that comprise applications and an operating system (see claim 1 above);

A SEPTIME

a processing unit coupled to the bus and running the operating system and applications by executing programming instructions, wherein the operating system provides computer system services through a tailored distinct one of a plurality of program structures (see claim 1 above), each tailored distinct program structure comprising:

a first programming interface for receiving service requests for a set of computer system I/O services of a first type (see s 1 and 3 above),

a first server coupled to receive service requests and to dispatch service requests to the computer system I/O services (see claim 3 above),

an activation model to define an operating environment in which a service request is to be serviced by the set of computer system I/O services (see claim 7 above), and

at least one specific instance of the set of computer system I/O services that operate within the activation model (see claim 8 above).

- 20. With respect to claim 10, the first programming interface is responsive to request from applications and from other program structures (see claim 6 above).

- 21. With respect to claim 12, the first server receives a message corresponding a service request from the first programming interface, maps the message into a function called by the client, and then calls the function (c17:36-54, subroutines in the I/O service framework are executed to provide data to the application program in response to the messages received).

- 22. With respect to claim 13, the message comprises a kernel message (c17:41-46).

Art Unit: 3992

- 23. With respect to claim 15, two or more I/O services share code or data (c9:1-11, code or data for SCSI service is shared by the SCSI framework and the Mass-Storage framework).

- 24. With respect to claim 16, said two or more I/O services are different types (see Figure 1).

- 25. With respect to claim 17, the program structure further comprises a storage mechanism to maintain identification of available services to which access is provided via the first server (c14:30-56).

- 26. With respect to claim 18, a computer implemented method of accessing I/O services of a first type, said computer implemented method comprising the steps of:

generating a service request for a first type of I/O services (see claims 1, 3, and 9 above);

a tailored distinct family server, operating in an operating system environment and dedicated to providing access to service requests for the first type of I/O service, receiving and responding to the service request based on an activation model specific to the first type of I/O services (see claims 1, 3, and 9 above); and

a processor running an instance of the first type of I/O services that is interfaces to the file server to satisfy the service request (see claims 1, 3, and 9 above).

Application/Control Number: 90/011,311

Art Unit: 3992

27. With respect to claim 19, the service request is generated by an application (see claim

7 above).

28. With respect to claim 20, the service request is generated by an instance of an I/O

service running in the operating system environment (see claim 7 above).

Examiner's Statement of Reasons for Patentability/Confirmation

29. Claims 11 and 14 are deemed to be patentable and/or confirmed over the prior

art of record for the following reasons:

30. Claim 11 recites the limitation "the first programming interface comprises at least one

library for converting functions into messages." Requester alleges that Andert discloses the

limitation at c10:1-6 ("A client 214 sends requests for services to a specific IO service

framework 102 associated with the client. The IO service framework 102 uses its associated

access manager 210 to load an appropriate device register with an appropriate command, such as

"write byte," "buffer a block," or whatever the appropriate action might be.") (see Request, p.

67). Requester asserts that "[t]hese commands, "write a byte" or "buffer a block," must reside in

a library." However, Requester provides no basis for this assertion. Andert discloses receiving

messages from application programs. In contrast, the claim requires the programming interface

to convert functions into messages (see the '131 patent specification, Figure 3, where a procedure

call from an application 302 is converted into a message by the library 303 at the interface 301).

Page 9

Art Unit: 3992

31. Claim 14 recites the limitation "said one of said at least one specific instances communicates to said another program structure of a second type using a message created using a library sent to the server of said another program structure." Andert does not disclose a message that is created using a library sent to the server.

### Service of Papers

32. After filing of a request for ex parte reexamination by a third party requester, any document filed by either the patent owner or the third party requester must be served on the other party (or parties where two or more third party requester proceedings are merged) in the reexamination proceeding in the manner provided in 37 CFR 1.248. The document must reflect service or the document may be refused consideration by the Office. See 37 CFR 1.550(f).

### Extensions of Time

33. Extensions of time under 37 CFR 1.136(a) will not be permitted in these proceedings because the provisions of 37 CFR 1.136 apply only to "an applicant" and not to parties in a reexamination proceeding. Additionally, 35 U.S.C. 305 requires that *ex parte* reexamination proceedings "will be conducted with special dispatch" (37 CFR 1.550(a)). Extensions of time in *ex parte* reexamination proceedings are provided for in 37 CFR 1.550(c).

### Litigation Reminder

34. The patent owner is reminded of the continuing responsibility under 37 CFR 1.565(a) to apprise the Office of any litigation activity, or other prior or concurrent proceeding, involving the

Application/Control Number: 90/011,311

Art Unit: 3992

patent throughout the course of this reexamination proceeding. The third party requester is also reminded of the ability to similarly apprise the Office of any such activity or proceeding throughout the course of this reexamination proceeding. See MPEP §§ 2207, 2282 and 2286.

Application/Control Number: 90/011,311

Art Unit: 3992

All correspondence relating to this ex parte reexamination proceeding should be directed as follows:

### By U.S. Postal Service Mail to:

Mail Stop *Ex Parte* Reexam

ATTN: Central Reexamination Unit

Commissioner for Patents

P.O. Box 1450

Alexandria, VA 22313-1450

By FAX to: (571) 273-9900

Central Reexamination Unit

By hand to: Customer Service Window

Randolph Building 401 Dulany St.

Alexandria, VA 22314

Any inquiry concerning this communication or earlier communications from the Reexamination Legal Advisor or Examiner, or as to the status of this proceeding, should be directed to the Central Reexamination Unit at telephone number (571) 272-7705.

/Woo H. Choi/ Reexamination Specialist Central Reexamination Unit 3992

EBK

Page 12

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Reexamination of

U.S. Patent No. 5,915,131

to KNIGHT, et al.

Reexam Control No. 90/011,311

Filed November 1, 2010

For: METHOD AND APPARATUS FOR HANDLING I/O REQUESTS UTILIZING SEPARATE PROGRAMMING INTERFACES TO ACCESS SEPARATE I/O SERVICES Confirmation No.: 1355

Art Unit: 3992

Examiner: CHOI, Woo

Atty. Docket No. 20142.0003.RXUS00

Mail Stop Ex Parte Reexamination Central Reexamination Unit Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

### **Patent Owner's Interview Summary**

Patent Owner thanks the Examiner for the courtesies extended during the May 27, 2011 Examiner Interview. A discussion took place in which the Patent Owner argued that Andert did not disclose a tailored distinct programming interface; that neither reference disclosed a plurality of servers as part of the operating system; and that Andert's Device Access Manager does not define an execution environment, but only regulates device access. The discussion focused on the meaning of claim terms. Patent Owner acknowledged the broadest reasonable interpretation standard, but pointed out that claim terms still must have a meaning that is reasonable in light of the specification, and that it is that understanding of the claim limitation that must be disclosed in the prior art to constitute anticipation. No agreement was reached.

The undersigned representative requests any extension of time that may be deemed necessary to further prosecution of this application.

The undersigned representative authorizes the Commissioner to charge any additional fees under 37 C.F.R. § 1.16 or 1.17 that may be required, or credit any overpayment, to Deposit Account 14-1437, referencing Attorney Docket No. 20142.0003.RXUS00.

In order to facilitate the resolution of any issues or questions resented by this paper, the Examiner may directly contact the undersigned by phone to further discussion.

### Respectfully submitted,

### /tracy w. druce/

Tracy W. Druce, Esq. Reg. No. 35,493

Brian K. McKnight, Esq. Reg. No. 59,914

C. Gideon Korrell, Esq. Reg. No. 60,131

Novak, Druce + Quigg LLP 1000 Louisiana Street, Suite 5300 Houston, Texas 77002 (713) 571-3400 (713) 456-2836 (fax) tracy.druce@novakdruce.com

### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Reexamination of

U.S. Patent No. 5,915,131

to KNIGHT, et al.

Reexam Control No. 90/011,311

Filed November 1, 2010

For: METHOD AND APPARATUS FOR HANDLING I/O REQUESTS UTILIZING SEPARATE PROGRAMMING INTERFACES TO ACCESS SEPARATE I/O SERVICES Confirmation No.: 1355

Art Unit: 3992

Examiner: CHOI, Woo

Atty. Docket No. 20142.0003.RXUS00

Mail Stop Ex Parte Reexamination Central Reexamination Unit Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

### Patent Owner's Response to Non-Final Office Action Under 37 C.F.R. §§ 1.111 and 1.550 in *Ex Parte* Reexamination

This paper is filed in response to the Non-Final Office Action mailed April 11, 2011 ("Office Action") in the above-captioned *ex parte* reexamination proceeding setting forth a shortened statutory period of two months in which to respond. Accordingly, this paper is timely filed on or before June 13, 2011 which is the next succeeding secular or business day which is not a Saturday, Sunday, or a Federal holiday after Saturday, June 11, 2011. 35 U.S.C. 21.

### I. Status of Claims

Claims 1-20 of U.S. Patent No. 5,915,131 (the '131 patent) are pending in this reexamination proceeding. Claims 1-10, 12, 13, and 15-20 stand rejected, and claims 11 and 14 are confirmed. In this response no claims have been amended. Patent Owner submits that all claims are in condition for confirmation, and therefore requests reconsideration and issuance of a Notice of Intent to Issue a Reexamination Certificate (NIRC) confirming all claims.

### II. Summary of Principal Arguments

There are fundamental differences between the invention claimed in the '131 patent and the Andert and Teaff references that form the basis of the Examiner's rejections. First, the Andert reference does not disclose, teach, or suggest "a first plurality of tailored distinct programming available to access a plurality of separate sets of I/O services provided through the operating system via service requests." Second, neither the Andert reference nor the Teaff reference discloses, teaches, or suggests "an operating system compris[ing] a plurality of servers." Third, the Andert reference does not disclose, teach, or suggest an "operating system [that] further comprises a plurality of activation models." Fourth, the Teaff reference does not disclose, teach, or suggest "[a] computer system comprising: a bus; at least one memory coupled to the bus . . .; and a processing unit coupled to the bus."

### III. All Rejected Claims are Patentable Over the Andert and Teaff References

In the Office Action, claims 1-6 were rejected under 35 U.S.C. § 102 as being anticipated by both the Andert and Teaff references. Additionally, claims 7-10, 12-13, and 15-20 were rejected under 35 U.S.C. § 102 as being anticipated by Andert only. However, neither of the references anticipates the claims because neither reference

discloses every element recited in the claims.<sup>1, 2</sup> Accordingly, Patent Owner respectfully traverses the rejections.

### A. Andert Does Not Disclose "a first plurality of tailored distinct programming interfaces"

Claim 3 recites, *inter alia*, "wherein an application has a first plurality of tailored distinct programming interfaces available to access a plurality of separate sets of I/O services provided through the operating system via service requests." The relevant section of the Office Action is provided below for reference:

wherein an application has a first plurality of tailored distinct programming interfaces (see Figure 1 and c8:30-44) available to access a plurality of separate sets of computer system services (c8:45-67) through the operating system (see Figure 5, applications 1030 access I/O services provided by Device Ensembles 1032 through the operating system 1014; see also c3:47-49) of the computer system via service requests (c1:59-62).

The Office Action asserts that Andert anticipates the claimed tailored distinct programming interfaces through Andert's Figure 1 and at col. 8, lines 30-44, where it shows and describes various I/O Service Frameworks. However, the I/O Service Frameworks in Andert are not a *tailored* distinct programming interface for accessing computer system services as recited in the claim because Andert does not disclose that the interfaces to the I/O System Framework are tailored.

<sup>&</sup>lt;sup>1</sup> Verdegaal Bros. v. Union Oil Co. of California, 814 F.2d 628, 631 (Fed. Cir. 1987) ("A claim is anticipated only if each and every element as set forth in the claim is found, either expressly or inherently described, in a single prior art reference."); Bristol-Myers Squibb Co. v. Danbury Pharm., Inc., 26 F.3d 138 (Fed. Cir. 1994) ("There must be no difference between the claimed invention and the anticipating reference as viewed by a person of ordinary skill in the art.") (citing Scripps Clinic & Research Fdn. v. Genetech, Inc., 927 F.2d 1565, 1576 (Fed. Cir. 1991)); Richardson v. Suzuki Motor Co., 868 F.2d 1226, 1236 (Fed. Cir. 1989) ("The identical invention must be shown in as complete detail as is contained in the . . . claim."); MPEP 2131.

<sup>&</sup>lt;sup>2</sup> Also, an ambiguous prior art reference is not anticipatory. *Mitsubishi Chemical Corp. v. Barr Labs., Inc.*, 718 F. Supp.2d 382,415-16 (citing *Eli Lilly & Co. v. Zenith Goldline Pharms., Inc.*, 364 F. Supp. 2d 820, 901 (S.D. Ind. 2005) (citing *In re Brink*, 57 C.C.P.A. 861, 419 F.2d 914, 918 (1970)), *aff'd*, 471 F.3d 1369 (Fed. Cir. 2006); *In re Turlay*, 49 C.C.P.A. 1288, 304 F.2d 893, 899 (1962) ("It is well established that an anticipation rejection cannot be predicated on an ambiguous reference."); *In re Hughes*, 52 C.C.P.A. 1355, 345 F. 2d 184, 188 (1965) ("[A]n ambiguous reference... will not support an anticipation rejection.").

<sup>&</sup>lt;sup>3</sup> Ctrl. No. 90/011,311, Office Action, mailed Apr. 11, 2011, at 5 (bold in original).

The plurality of I/O service frameworks disclosed in the Andert reference appear to provide applications access to the various I/O services offered through the operating system. The examples of I/O services disclosed by Andert include:

- (a) Mass Storage I/O services; (b) Keyboard processing services; (c) Mouse/Pointing device processing services;

- (d) SCSI services; (e) Serial communications port services;

- (f) Expansion bus management services; (g) Desktop bus I/O services; and (h) Power management services.<sup>4</sup>

By providing access to these operating system services, each of the I/O service frameworks presumably include interfaces, which might be considered distinct, but are not disclosed as being tailored, as those terms are used in the '131 patent.

The term "tailored" is used in both the claim and the specification without any special meaning beyond its dictionary definition.<sup>5</sup> In the context of claim 3, "tailored" refers to a programming interface<sup>6</sup> to a family of I/O services that is customized to meet the particular needs of that family.<sup>7</sup> Such an interpretation is consistent with both the original prosecution of the application that matured into the '131 patent's specification. <sup>10, 11</sup>

Specifically, the '131 patent states:

As a starting point, the proper interpretation of a claim limitation in reexamination must be assessed. While it is true that claim language is required to be given its broadest reasonable interpretation, it is also true that the interpretation must be 'consistent with the specification, . . . and that claim language should be read in light of the specification as it would be interpreted by one of ordinary skill in the art.'

In re Suitco Surface, 603 F.3d 1255, 1260 (Fed. Cir. 2010) (citing In re Bond, 910 F.2d 831, 833 (Fed.Cir.1990) (quoting In re Sneed, 710 F.2d 1544, 1548 (Fed.Cir.1983))).

<sup>&</sup>lt;sup>4</sup> Andert at 8:31-37.

<sup>&</sup>lt;sup>5</sup> See Exhibit B - The definition of "tailor" is "to cut, form, produce, alter, etc. so as to meet requirements or particular conditions; as her novel is *tailored* to popular tastes." Webster's New Twentieth Century Dictionary 1858 (2d ed. 1983).

<sup>&</sup>lt;sup>6</sup> An "application programming interface" is referred to in the `131 patent specification as "FPI" or "family programming interface."

<sup>&</sup>lt;sup>7</sup> Serial No. 08/435,677, Response, dated Sept. 2, 1997, at 4-5.

<sup>&</sup>lt;sup>8</sup> Serial No. 08/435,677, Response, dated Sept. 2, 1997, at 2-5.

<sup>&</sup>lt;sup>9</sup> Serial No. 08/435,677, Office Action, mailed Jan. 2, 1998, at 3.

<sup>&</sup>lt;sup>10</sup> The `131 patent at 6:20-36.

<sup>&</sup>lt;sup>11</sup> The Federal Circuit has recently explained that claim interpretation during patent reexaminations are only reasonable if consistent with the specification:

For example, when an application generates data for a video device, a display FPI <u>tailored</u> to the needs of video devices is used to gain access to display services. Likewise, when an application desires to input or output sound data, the application gains access to a sound family of services through an FPI. Therefore, the present invention provides family programming interfaces <u>tailored</u> to the needs of specific device families. <sup>12</sup>

Andert, however, does not disclose a programming interface that is tailored to the needs of the associated service. Andert is silent regarding the details of any interface made available by its I/O service frameworks beyond disclosing that they "represent an end user's interface to the I/O system," <sup>13</sup> and similar statements, which do not anticipate the claimed "tailored distinct programming interfaces."

In fact, it is probable that Andert's interface to its I/O service frameworks was not tailored. In the accompanying Declaration, David Wilson, Ph.D. explains that leading up to and at the time of the '131 patent's filing, typical interfaces to I/O services were limited to only a generic set of commands.<sup>14</sup>

However, regardless of the reason, Andert does not provide any description of its I/O service frameworks that can be considered a disclosure of "tailored distinct programming interfaces." As anticipation requires the reference to disclose each and every feature of the claim, Andert does not anticipate. Accordingly, Patent Owner submits that the rejection should be withdrawn.

While it has not been alleged in the current rejection, Patent Owner nevertheless notes that Andert does not anticipate the claim through any other application of the reference. Patent Owner notes that none of the other interfaces present in Andert could be considered to anticipate the claimed "tailored distinct programming interfaces" as none of the interfaces of Andert are disclosed as being tailored.

For example, Andert's Device Access Manager cannot have, or be itself considered the claimed tailored programming interfaces. While Andert indicates that a "one-size-fits-all" interface abstraction is not desirable when discussing the Device

<sup>&</sup>lt;sup>12</sup> The `131 patent at 6:29-36 (emphasis added).

<sup>&</sup>lt;sup>13</sup> Andert at 9:15-16.

<sup>&</sup>lt;sup>14</sup> See Exhibit A, Wilson Dec. ¶¶ 36-38.

Access Manager, Andert is discussing the functions of the Device Access Manager, not the interface to the Device Access Manager. 15

Furthermore, even if Andert's Device Access Manager had or was a tailored interface, the reference fails to disclose other elements of the claim. If Andert's Device Access Manager was cited against the "tailored distinct programming interfaces" claim limitation, nothing in Andert would disclose the claimed server, applications, or the plurality of activation models (in claim 7).

In conclusion, the rejection improperly alleges anticipation by Andert of the claimed: "a first plurality of tailored distinct programming interfaces" because the asserted I/O Service Frameworks in Andert are not disclosed to be tailored. Further, no other interface in Andert is disclosed as being tailored. Accordingly, Patent Owner submits that Andert does not anticipate claim 3.

Additionally, claim 1 recites the identical limitation and claims 9 and 18 recite a similar limitation and are patentable for the reasons discussed above with respect to claim 3. Claim 9 recites "wherein the operating system provides computer system services through a tailored distinct one of a plurality of program structures, each tailored distinct program structure comprising: a first programming interface for receiving service requests for a set of computer system I/O services of a first type." Claim 18 recites "a tailored distinct family server, operating in an operating system environment and dedicated to providing access to service requests for the first type of I/O service." Just as claim 3 is not anticipated by Andert, the respective rejections of claims 1, 9, and 18 also fail to anticipate because Andert's I/O Service Frameworks are not disclosed as being tailored or distinct. Accordingly, Patent Owner submits that Andert does not anticipate claims 1, 3, 9, 18, or any of their respective dependent claims.

<sup>&</sup>lt;sup>15</sup> Andert at 11:26-53.

### B. Andert Does Not Disclose "an operating system comprising a plurality of servers"

Claim 3 recites "wherein the operating system comprises a plurality of servers, and each of the first plurality of programming interfaces transfer service requests to one of the plurality of servers, wherein each of the plurality of servers responds to service requests from clients of the separate sets of I/O services." The Office Action alleges that Andert anticipates this limitation in the following way:

Andert discloses that the operating system comprises a plurality of servers (see Figures 1 and 2, I/O services frameworks), and each of the first plurality of programming interfaces transfer service requests to one of the plurality of servers, wherein each of the plurality of servers responds to service requests from clients of the separate sets of I/O services (see Figure 1, c 10:1-6). 16

These portions of the Andert reference cited in the Office Action do not make any mention of an operating system comprising a plurality of servers. Specifically, the Office Action cites to Figures 1 and 2 of Andert where it shows the I/O Service Frameworks which are presumably alleged to be the claimed servers. The Office Action however does not assert that Andert's I/O Service Frameworks are part of an operating system as required by the claim. This is most likely because Andert explains that the I/O Service Frameworks are not part of the operating system.

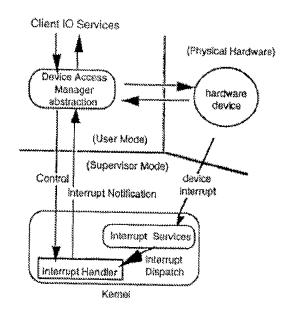

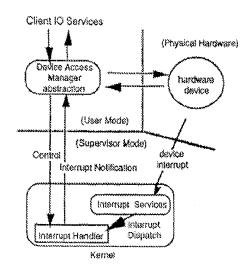

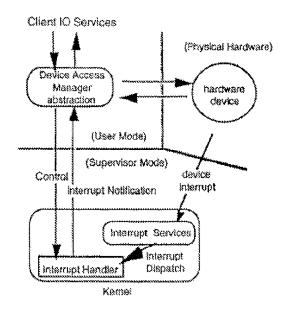

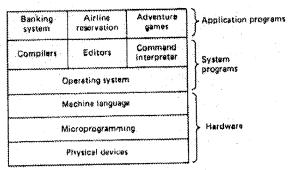

Andert specifically illustrates its I/O Service Frameworks as being outside the operating system.<sup>17</sup> For example, in Andert's Figure 3, below, the client I/O services shown communicating with the device access manager are illustrated as being in a user mode, which as Dr. Wilson discusses in his included Declaration, is another way of specifying that they are outside of the operating system.<sup>18</sup>

<sup>&</sup>lt;sup>16</sup> Ctrl. No. 90/011,311, Office Action, mailed Apr. 11, 2011, at 5 (bold in original).

<sup>&</sup>lt;sup>17</sup> Andert, at FIG. 3.

<sup>&</sup>lt;sup>18</sup> See Exhibit A, Wilson Dec. 99 40-41.

### FIGURE 3

Dr. Wilson explains that both the '131 patent and Andert draw a clear boundary between its user mode and its supervisor mode (operating system mode), and that both references use the user mode terminology consistently and the terminology has the same meaning in both documents. As Andert never discloses its I/O Service Frameworks as being in the operating system, Patent Owner asserts that the rejection should be withdrawn.

While it has not been alleged in the current rejection, Andert's Interrupt Services, which are illustrated to be in Andert's Supervisor Mode, cannot be the claimed servers. As Dr. Wilson discusses in the accompanying Declaration, he understands the '131 patent servers to receive service requests via an API from applications.<sup>20</sup> Since the interrupt services do not receive service requests from applications, the interrupt services cannot be the claimed service.

In conclusion, the Office Action incorrectly alleges that Andert discloses "the operating system comprises a plurality of servers" because Andert does not disclose that its I/O Service Frameworks are in the operating system. In

<sup>&</sup>lt;sup>19</sup> See Exhibit A, Wilson Dec. ¶¶ 12, and 40-41; see also Exhibit A Wilson Dec. at ¶¶ 10-14, and 17-19.

<sup>&</sup>lt;sup>20</sup> See Wilson Dec. ¶ 26.

fact, Andert specifically excludes the I/O Service Frameworks from the operating system. Accordingly, Patent Owner submits that Andert does not anticipate claim 3, or its dependent claims. Furthermore, independent claims 9 and 18 also recite limitations that require that servers be within the operating system. Claim 9 recites, "the operating system provides computer system services through a tailored distinct one of a plurality of program structures, each tailored distinct program structure comprising... a first server" and claim 18 recites "a tailored distinct family server, operating in an operating system environment." As claim 9 and 18 recite similar limitations as claim 3, they, and their respective dependent claims, are also patentable for the same reasons as claim 3 and its dependents. Accordingly, Patent Owner requests a NIRC confirming these claims.

### C. Teaff Does Not Disclose "the operating system comprises a plurality of servers"

Claim 3 recites "wherein the operating system comprises a plurality of servers, and each of the first plurality of programming interfaces transfer service requests to one of the plurality of servers, wherein each of the plurality of servers responds to service requests from clients of the separate sets of I/O services." The Office Action alleges that Teaff anticipates this limitation in the following way:

As discussed in his Declaration, Dr. Wilson explains that an operating system environment is the run time memory environment of the operating system. See Wilson Dec. ¶¶ 20-23.

each of the first plurality of programming interfaces transfer service requests to one of the plurality of servers, wherein each of the plurality of servers responds to service requests from clients of the separate sets of I/O services (see p. 4, Modularity and APIs and Figure 2; Appendix A). <sup>22</sup>

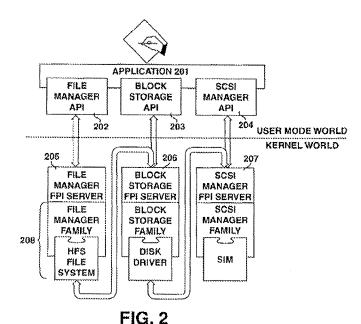

However, none of the cited sections disclose that the "operating system comprises a plurality of servers." Teaff's page 4 cited in the Office Action describes that Teaff's "HPSS architecture is highly modular," and that the "HPSS software components are loosely coupled" with APIs. Nothing in this portion of Teaff or the Office Action points to an operating system comprising a plurality of servers. The same is true in Teaff's Appendix A, which lists APIs to HPSS components. Figure 2 does illustrate a plurality of servers, but it does not show their relationship to the operating system. Further, Teaff's Figure 2 shows servers as being HPSS components, and as discussed in detail below, Teaff's HPSS application layer is separate from the operating system. Patent Owner submits that the rejection fails to anticipate claim 3 because it does not show that Teaff discloses that the "operating system comprises a plurality of servers," as claimed.

The Teaff reference discloses what it calls a High Performance Storage System in which client requests are directed by an HPSS server to network-attached storage devices through a high-speed data transfer network. In the HPSS system, clients gain access to the networked storage devices by accessing the HPSS server through an API. Teaff never discloses that its HPSS servers are part of the operating system, and never discloses that the HPSS system is itself an operating system. Rather Teaff actually indicates the opposite. As illustrated in Teaff's Figure 3 below, HPSS is shown to be situated several layers above and indeed separate from the operating system.

<sup>&</sup>lt;sup>22</sup> Ctrl. No. 90/011,311, Office Action, mailed Apr. 11, 2011, at 3 (bold in original).

<sup>&</sup>lt;sup>23</sup> Teaff, at 3.

Figure 3 - HPSS DCE Architecture Infrastructure

Further, the HPSS itself cannot be considered an operating system. HPSS utilizes services from the layers below such as the DCE (distributed computing environment standard) and the operating system, <sup>24, 25</sup> and such behavior is inconsistent with a view of the HPSS being considered an operating system. <sup>26</sup>

In fact, Teaff does not anticipate the claim because including the servers in an operating system was antithetical to Teaff's explicit design objective.<sup>27</sup> Specifically Teaff states:

Another important design goal is portability to many vendor's platforms to enable OEM and multivendor support of HPSS. HPSS has been designed to run under Unix requiring no kernel modifications, and to use standards based protocols, interfaces, and services where applicable.<sup>28</sup>

In the passage above, Teaff clearly states that it is designed to be portable to many vendor's platforms, and therefore Teaff would not want to limit the use of its servers to one specific operating system.

<sup>&</sup>lt;sup>24</sup> See Teaff, p. 4 ("These requirements are accomplished using a client/server architecture, the use of OSF's DeE as its distributed infrastructure, support for distributed file system interfaces and multiple servers.")

<sup>&</sup>lt;sup>25</sup> See Teaff, p. 7 ("HPSS uses OSF's DCE as the base infrastructure for its distributed architecture.")

<sup>&</sup>lt;sup>26</sup> See Exhibit A, Wilson Dec. ¶ 45.

<sup>&</sup>lt;sup>27</sup> See Exhibit A, Wilson Dec. ¶ 46.

<sup>&</sup>lt;sup>28</sup> Teaff, at 5.

In conclusion, Teaff does not disclose "wherein the operating system comprises a plurality of servers, and each of the first plurality of programming interfaces transfer service requests to one of the plurality of servers, wherein each of the plurality of servers responds to service requests from clients of the separate sets of I/O services" as claimed. Further, the limitation is antithetical to Teaff's specific design objectives to work in a layer under the operating system. Accordingly, Patent Owner submits that Teaff does not anticipate claim 3, or its dependents. Accordingly, Patent Owner requests a NIRC confirming these claims.

### D. Andert Does Not Disclose "the operating system comprises a plurality of activation models"

Claim 7 recites, *inter alia*, "[t]he computer system defined in claim 3 wherein the operating system further comprises a plurality of activation models." Regarding Andert, the Office Action asserts:

With respect to claim 7, the operating system further comprises a plurality of activation models, wherein each of the plurality of activation models is associated with one of the plurality of servers to provide a runtime environment for the set of I/O services to which access is provided by said one of the plurality of servers (c 11:25-58).

The Office Action asserts that Andert discloses the claimed activation model by way of Andert's Device Access Manager. However, the activation model is claimed to be in the operating system while the Device Access Manager resides outside the operating system in user space.

Andert requires that the Device Access Manager reside outside of the operating system. Similar to the discussion above with respect to servers, Andert places its Device Access Manger in the user space as illustrated in its FIG. 3, below.

<sup>&</sup>lt;sup>29</sup> Ctrl. No. 90/011,311, Office Action, mailed Apr. 11, 2011, at 6. (bold in original)

FIGURE 3

Accordingly, Andert explicitly places its Device Access Manager outside its operating system, unlike the claimed activation model, which is recited as being comprised in the operating system; therefore Andert does not anticipate this limitation of the claim.

More fundamentally, the activation model is just a model while the Device Access Manager is actual executable code. The activation model is defined by the claims as a model associated with one of the plurality of servers to provide a runtime environment for the set of I/O services. This is different from Andert's Device Access Manager that executes hardware access tasks. Andert describes the Device Access Manager as "user-mode abstractions that execute outside the kernel and are charged with all tasks performing tasks associated with hardware access." Andert explains that some of the tasks performed by the Device Access Manager include: install and remove Interrupt Handlers, makes buffers ready for I/O, unlocks client's resident I/O buffers, and informs clients through the I/O service framework of completed tasks. The activation model, on the other hand, does not perform tasks; rather, as explained

<sup>&</sup>lt;sup>30</sup> Andert, at 9:49-51.

<sup>31</sup> Andert, at 10:42-43.

<sup>&</sup>lt;sup>32</sup> Andert, at 11:4-6.

<sup>&</sup>lt;sup>33</sup> Andert, at 11:19-20.

<sup>&</sup>lt;sup>34</sup> Andert, at 11:20-22.

above, it defines the runtime environment. It is something that executables reference to. Accordingly, the Device Access Manager does not disclose the claimed activation models.

In conclusion, the Office Action incorrectly alleges that Andert discloses "the operating system further comprises a plurality of activation models" because Andert does not disclose that its Device Access Manager, which is cited against the claimed activation models, is in the operating system. In fact, Andert specifically places the Device Access Manager in user space, and therefore outside the protection of the operating system. Accordingly, Patent Owner submits that Andert does not anticipate claim 7, or its dependent claim. Independent claims 9 and 18 also recite limitations that require that activation models be within the operating system. Claim 9 recites, "the operating system provides computer system services through a tailored distinct one of a plurality of program structures, each tailored distinct program comprising... an activation model to define an operating environment" and claim 18 recites "a tailored distinct family server, operating in an operating system environment dedicated to providing access to service requests for the first type of I/O service, receiving and responding to the service request based on an activation model specific to the first type of I/O services." 35 As claim 9 and 18 recite similar limitations as claim 7, they, and their dependent claims, are also patentable for the same reasons as claim 7 and its dependents. Accordingly, Patent Owner requests a NIRC confirming these claims.

As discussed in his Declaration, Dr. Wilson explains that an operating system environment is the run time memory environment of the operating system. See Wilson Dec. ¶¶ 20-23.

### E. Teaff Does Not Disclose "A computer system comprising: a bus."

Claim 1 recites, *inter alia*, "A computer system comprising: a bus; at least one memory coupled to the bus...; and a processing unit coupled to the bus." Regarding Teaff, the Office Action asserts:

Teaff discloses a computer system (p. 3, Figure 1) comprising:

**a bus** (Figure 1, control buses that connect network elements and workstations to the HPSS servers; also, a bus is an inherent component of a computer system);

at least one memory (Figure 1, network attached memories or other memories in servers and workstations) coupled to the bus for storing data and programming instructions that include applications and an operating system; and

a processing unit (Figure 1, servers and workstations) coupled to the bus and running the operating system and applications by executing programming instructions (see pp. 4-5, Modularity and APIs, and Portability and Standards), wherein an application has a first plurality of tailored distinct programming interfaces (p. 4, "The HPSS software components are loosely coupled, with open application program interfaces (APIs) defined at each component level"; see also Appendix A for a list of tailored APIs)<sup>36</sup>

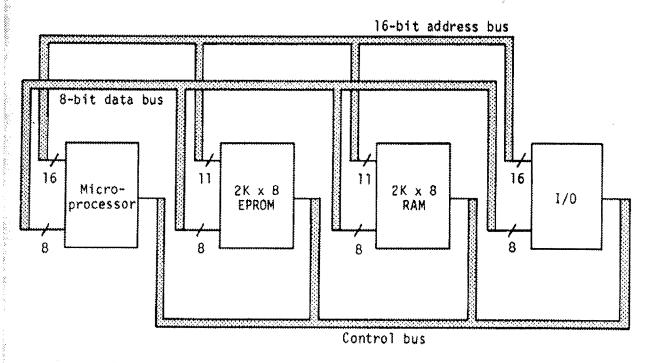

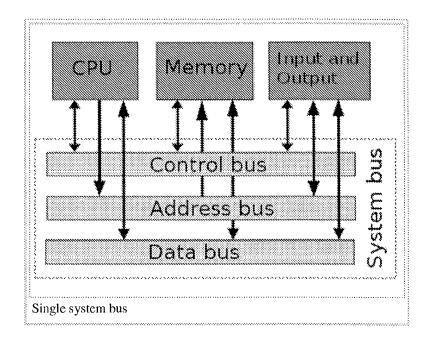

A bus, as that term was understood by persons of ordinary skill in the art when the '131 patent was filed, is a collection of parallel wires directly connected to a processor and other computer hardware components.<sup>37</sup>

The Office Action asserts that Teaff discloses a bus in two possible applications of Teaff. The first application of Teaff matches the understanding of a person of ordinary skill in the art for a bus as stated above; that is, the recited bus is inherently disclosed as a component of a computer system. Even under this application of Teaff, it does not

<sup>&</sup>lt;sup>36</sup> Ctrl. No. 90/011,311, Office Action, mailed Apr. 11, 2011, at 2-3. (bold in original)

<sup>&</sup>lt;sup>37</sup> See Exhibit A, Wilson Dec. ¶¶ 27-30.

anticipate when the entire claim is considered, which is required for an anticipation rejection; that is, Teaff does not disclose "a processing unit" having all of the recited limitations, and that is coupled to the bus.

Under another application of Teaff, the Office Action asserts that Teaff's control network is a bus, but this is inconsistent with a person of ordinary skill in the art's understanding of a bus when the '131 patent was filed, and therefore, this application of Teaff also does not anticipate the claim. The rejection does not allege that every element of the claim resides on the same computer as would be required even if an inherently disclosed bus were asserted from one of Teaff's computers. Still, every element of the claim must be disclosed in Teaff as being on that same computer. The rejection fails to identify a specific computer that is disclosed as having a bus connected to a memory and to a processing unit having the characteristics recited in the claim. In fact, the rejection argues the opposite by citing to Teaff's sections "Modularity and APIs", and "Portability and Standards," which discloses that HPSS software components are distributed (i.e., not on the same computer). In these sections Teaff does acknowledge flexibility in its distributed system in that components can be moved to other platforms, but Teaff never discloses a single computer that meets the claimed limitations, and accordingly does not anticipate the claim.

The rejection also improperly alleges that Teaff's control network anticipates the claimed bus. At the time the '131 patent was filed, a network connection was not considered to be a bus. <sup>39,40</sup> In his Declaration, Dr. Wilson discusses that at least until 1998, a bus was known by persons of ordinary skill in the art to be a collection of parallel wires directly connected to a processor and other computer hardware components. <sup>41</sup> This understanding of what a bus was at the time the '131 patent was filed is consistent with the '131 patent's specification; in particular, its description of the computer system

<sup>&</sup>lt;sup>38</sup> See MPEP 2131 citing In re Bond, 910 F.2d 831, 15 USPQ2d 1566 (Fed. Cir. 1990) ("The elements must be arranged as required by the claim, but this is not an ipsissimis verbis test, i.e., identity of terminology is not required.").

<sup>&</sup>lt;sup>39</sup> See Exhibit A, Wilson Dec. ¶ 31.

<sup>&</sup>lt;sup>40</sup> See, Exhibit C, Wikipedia - Bus (computing), http://en.wikipedia.org/wiki/Bus\_(computing) - (last modified on May 25, 2011).

<sup>&</sup>lt;sup>41</sup> See Exhibit A, Wilson Dec. ¶¶ 27-30.

illustrated in FIG. 1. Teaff's control network as described was not a bus as that term was understood by persons of ordinary skill in the art at the time the '131 patent was filed. Rather Teaff's control network is a network connection, which does not describe the claimed bus as those terms were understood at the time the '131 patent was filed.

In conclusion, Teaff does not anticipate claim 1 under either of the two alternative application of Teaff asserted in the Office Action. While a bus may be an inherent component of a computer, when an internal bus is alleged to anticipate the claim, Teaff fails to disclose the rest of the recited elements of the claim. Second, Teaff's control network is not a bus, and therefore does not anticipate that claim element.

#### IV. Conclusion

It is respectfully asserted that the rejections have been properly traversed. Patent Owner therefore respectfully requests that the Examiner reconsider all presently outstanding rejections and that they be withdrawn. Patent Owner believes that a full and complete reply has been made to the outstanding Office Action and, as such, the present reexamination proceeding is in condition for a Notice of Intent to Issue a Reexamination Certificate (NIRC). If Examiner believes, for any reason, that personal communication will expedite prosecution of this reexamination proceeding, the Examiner is invited to telephone the undersigned at the number provided.

Prompt and favorable consideration of this Response is respectfully requested.

\* \* \* \* \* \*

The undersigned representative requests any extension of time that may be deemed necessary to further prosecution of this application.

The undersigned representative authorizes the Commissioner to charge any additional fees under 37 C.F.R. § 1.16 or 1.17 that may be required, or credit any overpayment, to Deposit Account <u>14-1437</u>, referencing Attorney Docket No. 20142.0003.RXUS00.

In order to facilitate the resolution of any issues or questions resented by this paper, the Examiner may directly contact the undersigned by phone to further discussion.

### Respectfully submitted,

### /tracy w. druce/

Tracy W. Druce, Esq. Reg. No. 35,493

Brian K. McKnight, Esq. Reg. No. 59,914

C. Gideon Korrell, Esq. Reg. No. 60,131

Novak, Druce + Quigg LLP 1000 Louisiana Street, Suite 5300 Houston, Texas 77002 (713) 571-3400 (713) 456-2836 (fax) tracy.druce@novakdruce.com

# Exhibit A – Declaration of David A. Wilson, Ph.D.

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Reexamination of

U.S. Patent No. 5,915,131

to KNIGHT, et al.

Reexam Control No. 90/011,311

Filed November 1, 2010

For: METHOD AND APPARATUS FOR HANDLING I/O REQUESTS UTILIZING SEPARATE PROGRAMMING INTERFACES TO ACCESS SEPARATE I/O SERVICES Confirmation No.: 1355

Art Unit: 3992

Examiner: CHOI, Woo

Atty. Docket No. 20142.0003.RXUS00

Attn: Central Reexamination Unit Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

### Declaration of David A. Wilson, Ph.D. Under 37 C.F.R. § 1.132

#### I, David A. Wilson, Ph.D., declare as follows:

- 1. I have been retained on behalf of Apple Inc. ("Apple"), the Patent Owner in the above captioned reexamination. I understand that this reexamination involves U.S. Patent No. 5,915,131 ("the '131 patent") entitled "Method and Apparatus for Handling I/O Requests Utilizing Separate Programming Interfaces to Access Separate I/O Services."

- 2. I have reviewed and am now familiar with the specification of the '131 patent filed on May 5, 1995.

- 3. I have reviewed and am now familiar with the Office Action dated April 11, 2011 issued by the U.S. Patent and Trademark Office ("USPTO") for the '131 patent ("Office Action"). I understand that claims 11 and 14 have been confirmed and claims 1-10, 12, 13, and 15-20 have been rejected in this reexamination proceeding.

- 4. I have reviewed and am now familiar with U.S Patent No. 5,566,346 to Andert et al. ("Andert") which is a document applied under one 35 U.S.C. § 102 rejection set forth in the Office Action.

- 5. I have also reviewed and am now familiar with *The Architecture of the High Performance Storage System* by Danny Teaff et al. ("Teaff") which is a document applied under another 35 U.S.C. § 102 rejection set forth in the Office Action.

- 6. In making the statements, and reaching my opinions and conclusions stated herein, I have considered Andert, Teaff, and the '131 patent, including portions of its file history, in the context of my own education, training, research, knowledge, and personal and professional experience.